Dissertation zur Erlangung des Doktorgrades der Technischen Fakultät der Albert-Ludwigs-Universität Freiburg im Breisgau

# Design and Implementation of Cause-Based and Consequence-Based Control Circuits for Active Charge Balancing in CMOS Integrated Neural Stimulator

M.Sc. Natalie Butz

August, 2021

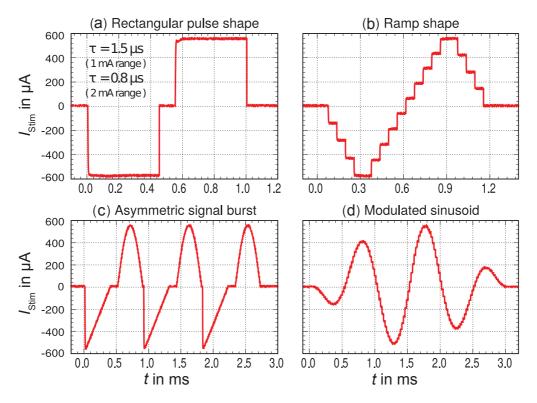

Albert-Ludwigs-Universität Freiburg im Breisgau Technische Fakultät Institut für Mikrosystemtechnik

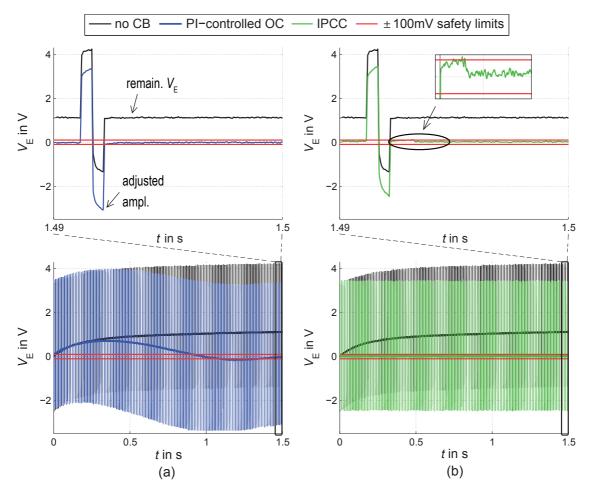

#### Dekan

Prof. Dr. Rolf Backofen

## Referenten

Prof. Dr.-Ing. Yiannos Manoli Prof. Dr. Thomas Stieglitz

## Datum der Promotion

22.03.2021

"Do. Or do not. There is no try." (Yoda)

# **Contents**

| Ab | strac | t                                                            | 1  |

|----|-------|--------------------------------------------------------------|----|

| Zυ | ısamı | menfassung                                                   | 3  |

| 1. | Intro | oduction                                                     | 5  |

|    | 1.1.  | Functional Electrical Stimulation                            | 5  |

|    | 1.2.  | Motivation                                                   | 6  |

|    |       | 1.2.1. Importance of Charge Balancing                        | 6  |

|    |       | 1.2.2. Further Benefits and Applications of Charge Balancing | 7  |

|    | 1.3.  | Thesis Organization                                          | 9  |

| 2. | Fund  | damentals                                                    | 11 |

|    | 2.1.  | Biomedical Background                                        | 11 |

|    |       | 2.1.1. Anatomy of Nerves                                     | 11 |

|    |       | 2.1.2. Physiological Nerve Excitation                        | 13 |

|    | 2.2.  | Technical Nerve Excitation                                   | 15 |

|    |       | 2.2.1. Charge Delivery Strategies                            | 16 |

|    |       | 2.2.2. Electrodes                                            | 18 |

|    |       | 2.2.3. Selectivity                                           | 20 |

|    | 2.3.  | Electrode-Tissue Interface                                   | 21 |

|    |       | 2.3.1. Charge Transfer at the Phase Boundary                 | 21 |

|    |       | 2.3.2. Equivalent Electrical Model                           | 22 |

|    |       | 2.3.3. Remaining Charges and Safety Limits                   | 23 |

|    | 2.4.  | Summary                                                      | 26 |

| 3. | Stat  | e-of-the-Art Charge Balancing                                | 27 |

|    | 3.1.  | Blocking Capacitors                                          | 28 |

|    | 3.2.  | Consequence-Based Charge Balancing Methods                   | 29 |

|    |       | 3.2.1. Passive Charge Balancing                              | 30 |

|    |       | 3.2.2. Short Pulse Insertion                                 | 30 |

|    | 3.3.  | Cause-Based Charge Balancing Methods                         | 31 |

|    |       | 3.3.1. Stimulus Matching                                     | 32 |

|    |       | 3.3.2. Offset Compensation                                   | 33 |

|    | 3 /   | Summary                                                      | 25 |

| 4. |      | erall System Description and Stimulator Front-End                | 37 |

|----|------|------------------------------------------------------------------|----|

|    | 4.1. | V I                                                              |    |

|    | 4.2. | •                                                                |    |

|    | 4.3. | <del></del>                                                      |    |

|    |      | 4.3.1. Regulated Input Cascode Current Mirror                    |    |

|    |      | 4.3.2. Current DAC Design and Implementation                     |    |

|    |      | 4.3.3. Stability Considerations                                  |    |

|    |      | 4.3.4. Measurement Results                                       |    |

|    |      | 4.3.5. Comparison to State-of-the-Art Stimulator Front-Ends      |    |

|    | 4.4. |                                                                  |    |

|    |      | 4.4.1. Design Considerations                                     |    |

|    |      | 4.4.2. Simulation and Measurement Results                        |    |

|    | 4.5. | Summary                                                          | 59 |

| 5. | PI-0 | Controlled Offset Compensation                                   | 61 |

|    | 5.1. | Conceptual Overview                                              | 61 |

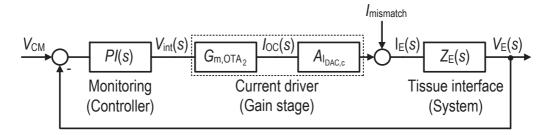

|    | 5.2. | Controller Considerations                                        | 63 |

|    | 5.3. | Components Design and Characterization                           | 65 |

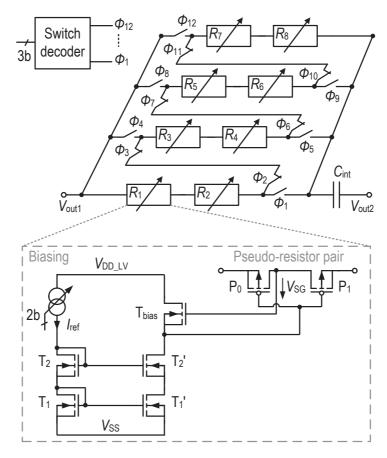

|    |      | 5.3.1. PI Controller                                             | 66 |

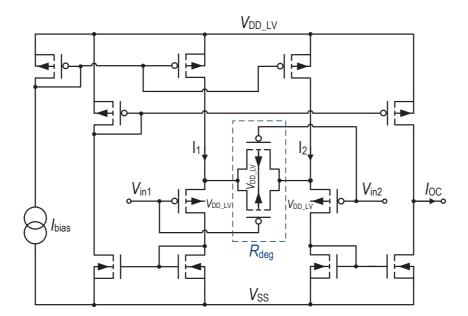

|    |      | 5.3.2. Current Driver                                            | 73 |

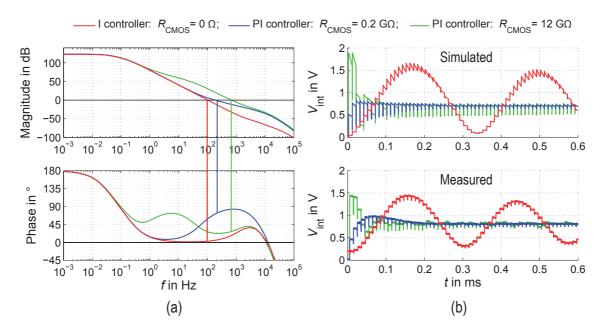

|    | 5.4. | Stability Considerations                                         | 74 |

|    | 5.5. | Measurement Results                                              | 77 |

|    |      | 5.5.1. System Measurements                                       | 77 |

|    |      | 5.5.2. In-Vitro Measurements                                     | 78 |

|    | 5.6. | Comparison to State-of-the-Art Cause-Based Systems               | 80 |

|    | 5.7. | Summary                                                          | 82 |

| 6. | Inte | r-Pulse Charge Control                                           | 83 |

|    | 6.1. | Conceptual Overview                                              | 83 |

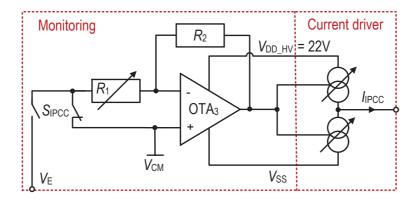

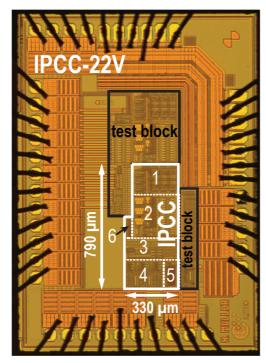

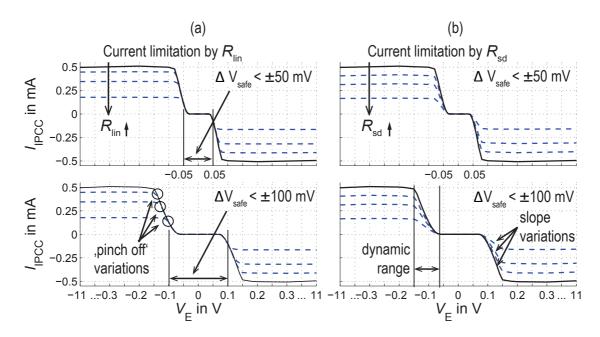

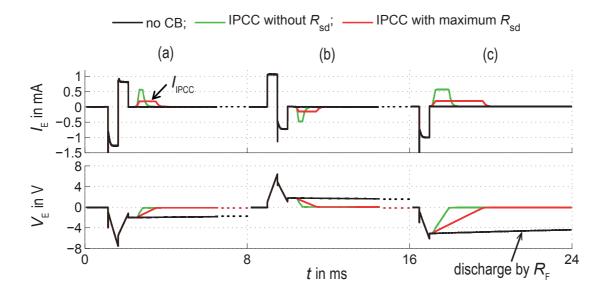

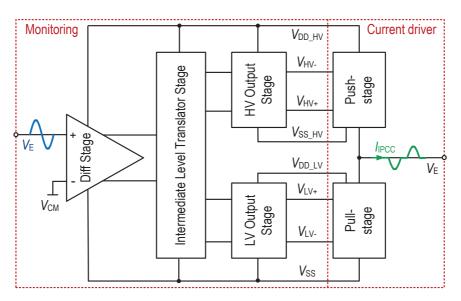

|    | 6.2. | IPCC with 22 V Compliance                                        | 86 |

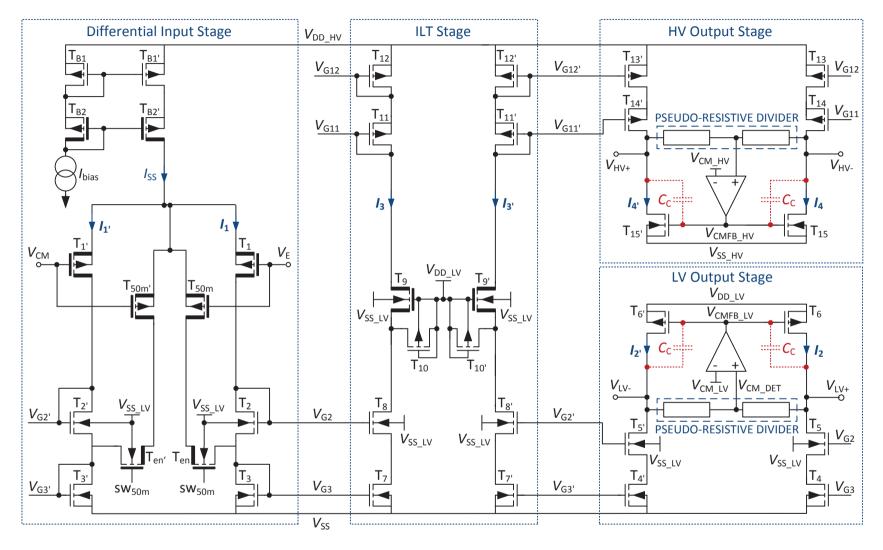

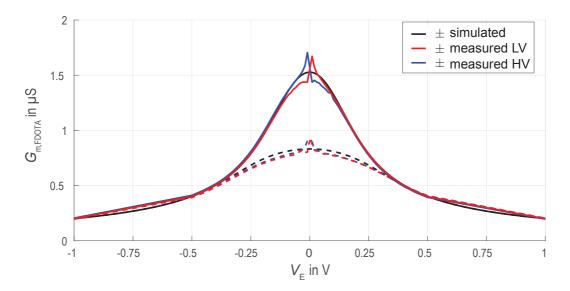

|    |      | 6.2.1. Operational Transconductance Amplifier                    | 87 |

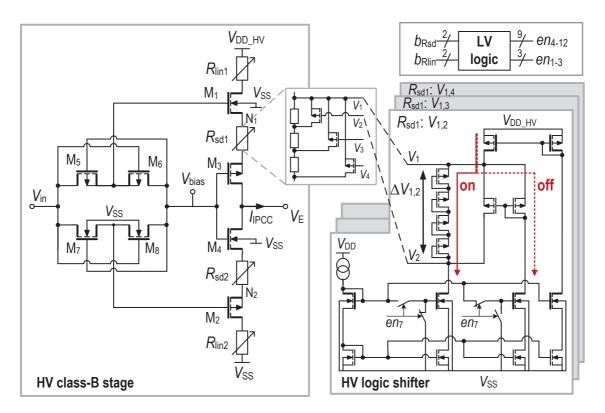

|    |      | 6.2.2. Advanced Class-B Stage                                    | 88 |

|    |      | 6.2.3. Measurement Results                                       | 90 |

|    | 6.3. | IPCC with Adaptive Supply Compliance                             | 94 |

|    |      | 6.3.1. Fully Differential Operational Transconductance Amplifier |    |

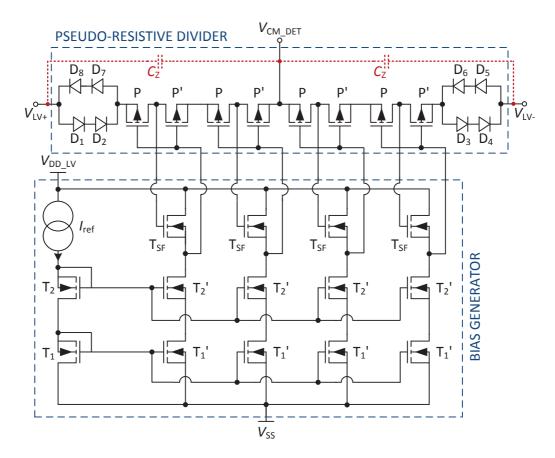

|    |      | 6.3.2. CMFB Circuit                                              |    |

|    |      | 6.3.3. Split-Bias Class-B Stage                                  | 99 |

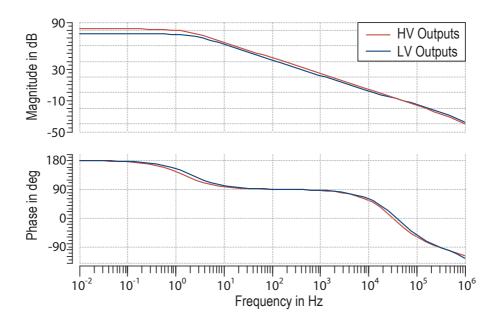

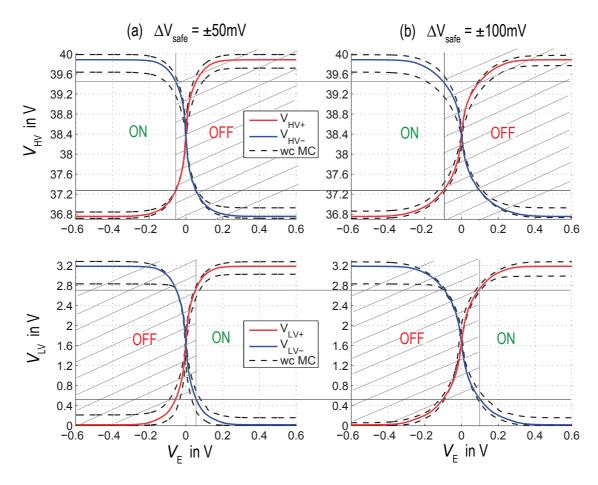

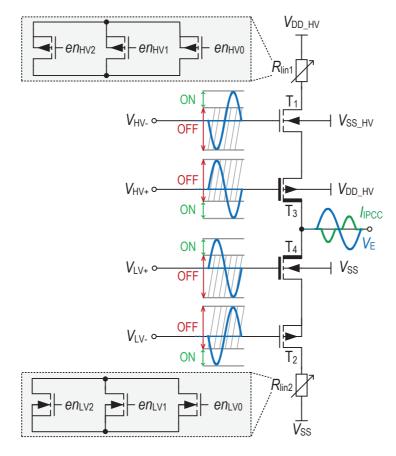

|    |      | 6.3.4. Simulated System Results                                  |    |

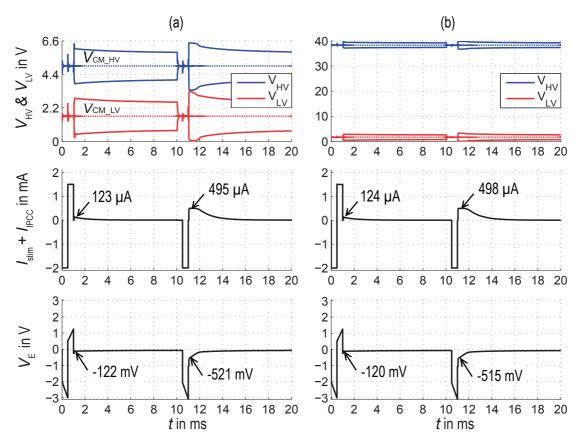

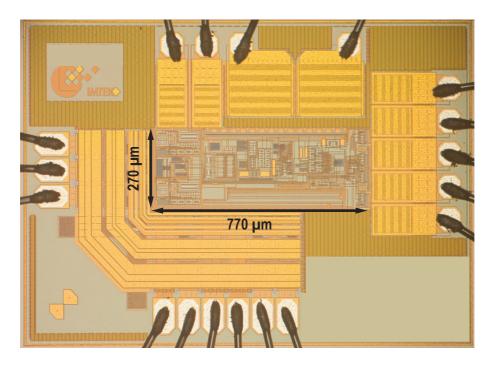

|    |      | 6.3.5. Measurement Results                                       |    |

|    | 6.4. | Stability Considerations                                         |    |

|    | 6.5. | Comparison to State-of-the-Art Consequence-Based Systems         |    |

|    |      | Summary                                                          |    |

| 7. | Twi   | n-Track Charge Balancer        | 111   |

|----|-------|--------------------------------|-------|

|    | 7.1.  | Twin-Track System Setup        | . 111 |

|    | 7.2.  | Twin-Track Measurement Results | . 114 |

|    |       | 7.2.1. System Measurements     | . 114 |

|    |       | 7.2.2. In-Vitro Measurements   | . 114 |

|    | 7.3.  | Summary                        | . 117 |

| 8. | Con   | clusion and Outlook            | 119   |

|    | 8.1.  | Conclusion                     | . 119 |

|    | 8.2.  | Outlook                        | . 121 |

| Ac | know  | ledgments                      | 123   |

| Α. | Арр   | endix                          | 125   |

|    | A.1.  | Complementary Calculations     | . 125 |

|    | A.2.  | FPGA Usage for Measurements    | . 126 |

| В. | Autl  | nor's Scientific Track         | 129   |

|    | B.1.  | Publications and Presentations | . 129 |

|    | B.2.  | Patents                        | . 130 |

|    | B.3.  | Supervised Thesis              | . 130 |

| Bi | bliog | raphy                          | 131   |

| No | men   | clature                        | 139   |

# **Abstract**

The treatment of neurological disorders and muscular disabilities is a challenging task. Functional electrical stimulation (FES) and functional neural stimulation (FNS), which excite nerves artificially by electrical charges, are impressive achievements for improving daily life quality of impaired patients. Two well-established examples are cardiac pacemakers and cochlear implants. In order to avoid charge accumulation at the electrode-tissue interface, which causes tissue lesion and electrode corrosion, charge balancing has become a major theme in safe electrical stimulation. Using biphasic current pulses, the main transferred charge is compensated by reversing the current direction within a stimulus. However, due to process variations in integrated circuits, mismatch in the biphasic waveform always occurs, hence, charge balancing as an additional safety aspect is indispensable. For reliability reasons, most certified medical devices are equipped with blocking capacitors or passive charge balancing, despite their large size, long settling time, and uncontrolled charge compensation. A promising approach towards small, fast, and well-controlled charge compensation is closed loop active charge balancing.

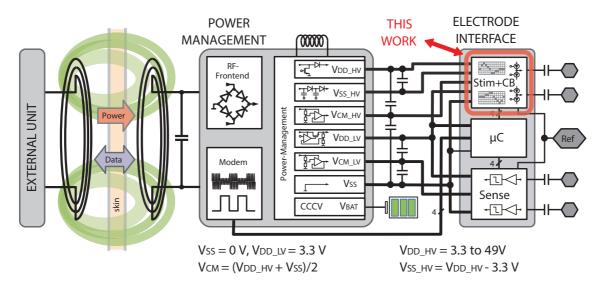

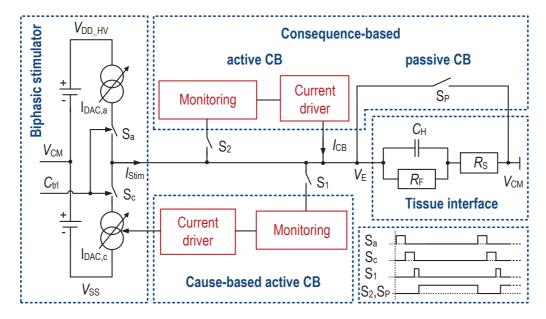

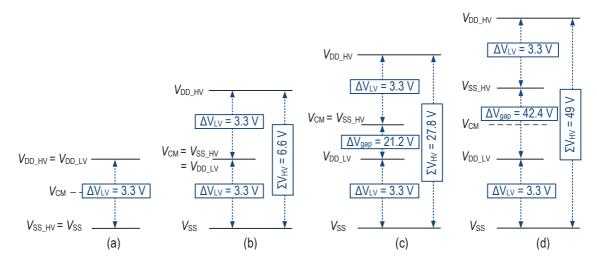

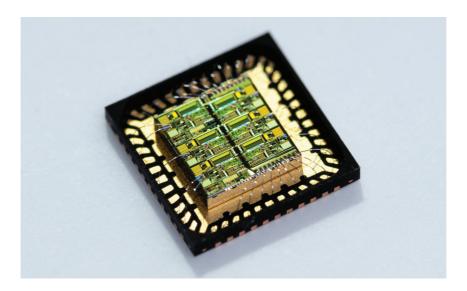

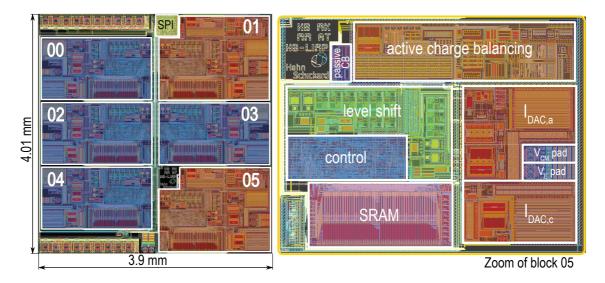

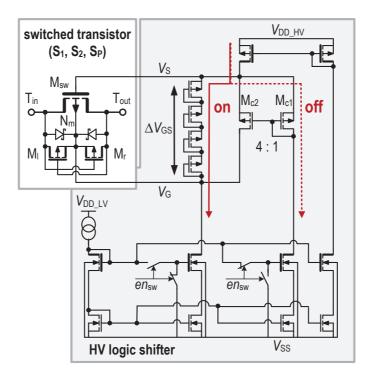

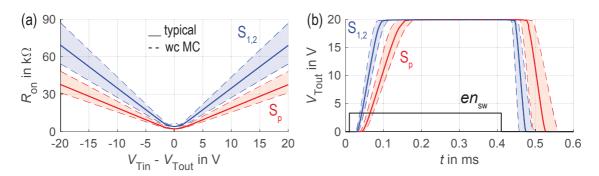

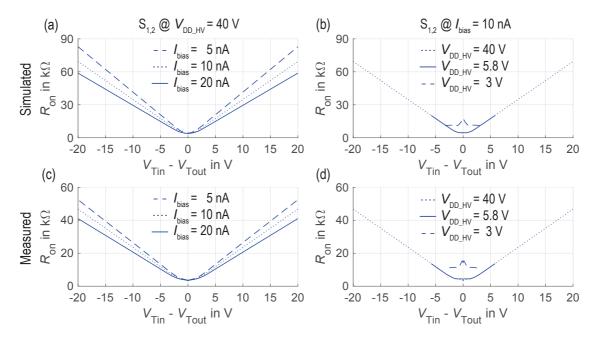

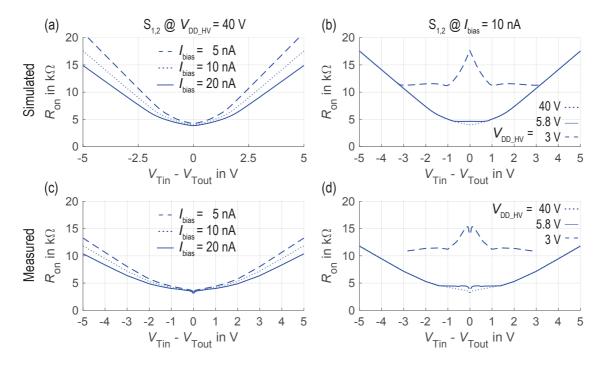

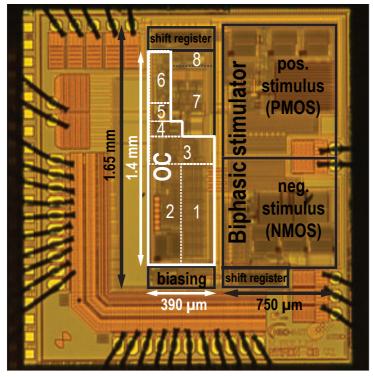

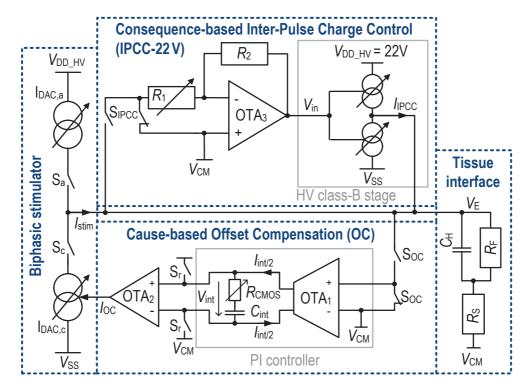

This thesis presents the author's research activities on the development of novel, CMOS integrated, low-power, high-voltage (HV) compatible, active charge balancing systems. Additionally, the thesis comprises the author's contribution to the development of a HV switch and an analog front-end neural stimulator that is used for all measurements to demonstrate the performance of the presented active charge balancing systems. Modern implantable stimulators have become highly specialized and adjustable to the challenges of diverse applications. Therefore, the developed, power-efficient and current-controlled stimulator is capable of supplying arbitrary programmable current pulse shapes and provides a HV compliance of up to 49 V. The stimulator is equipped with active charge balancing and passive charge balancing by a novel CMOS integrated HV switch. The main focus of this thesis lies on the development and implementation of the active charge balancing systems.

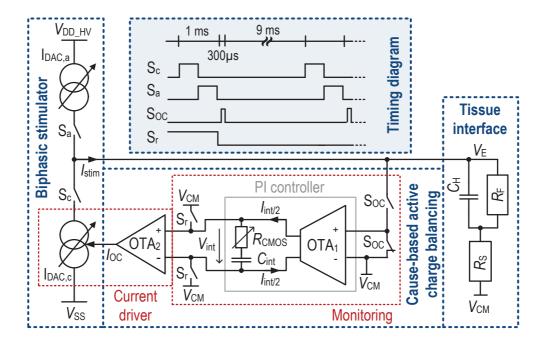

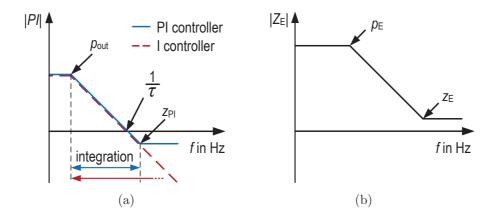

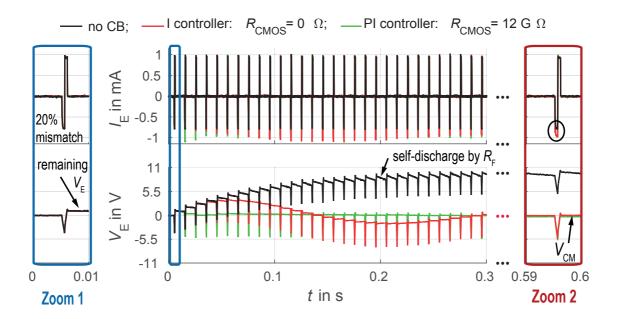

The first balancer presented provides long-term charge balancing, achieved by a cause-based proportional-integral (PI)-controlled Offset Compensation of the remaining electrode voltage. Here, the value of the remaining electrode voltage is monitored and serves as a measure for the stimuli mismatch. Thus, the amplitude of the cathodic current pulse of the presented stimulator front-end is adjusted accordingly. The system is very power-efficient and HV-robust. The balancer's monitoring amplifier provides an extraordinary small transconductance, which led to the first integrated PI controller for offset compensation in neural implants. Sev-

eral controller options are available to adapt to different electrode impedances, for which a detailed close loop stability analysis is presented.

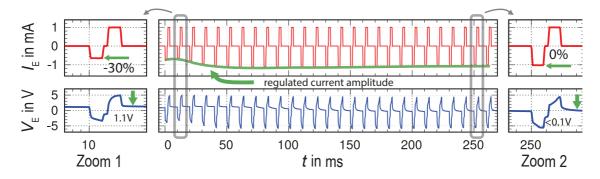

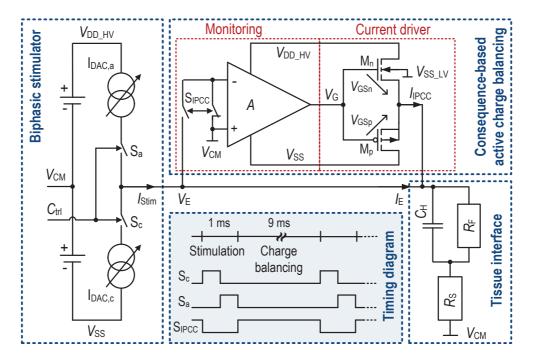

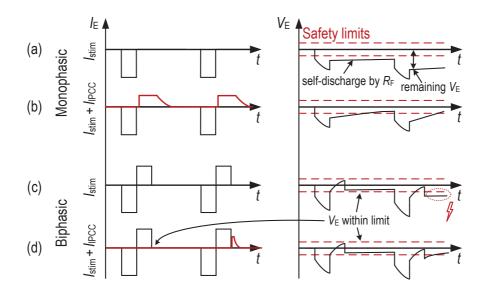

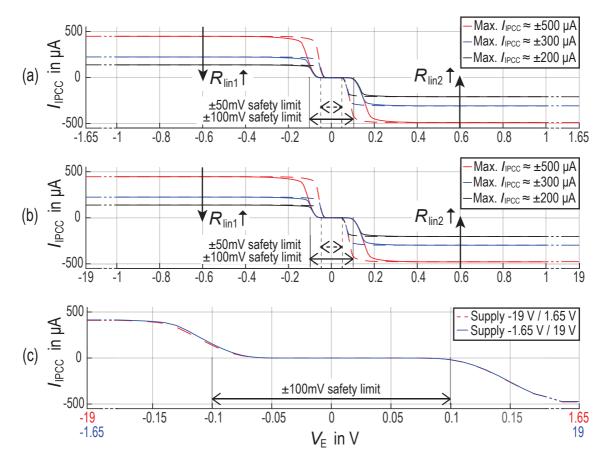

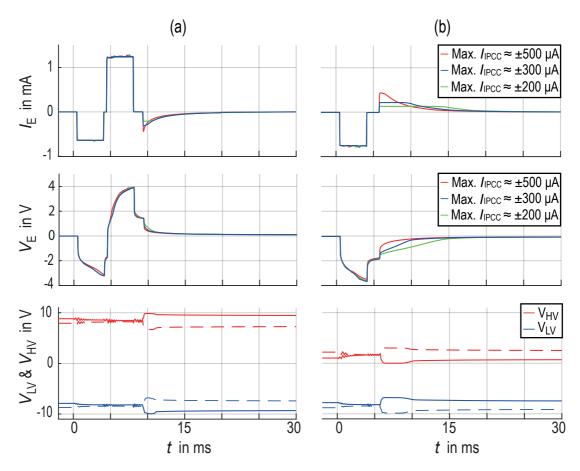

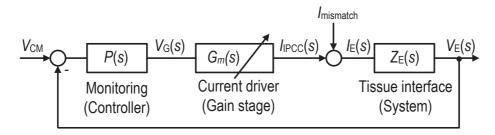

Instantaneous autonomous balancing is realized by another, novel concept, the consequence-based Inter-Pulse Charge Control (IPCC). A class-B architecture is used to supply the compensation currents. In the implemented way, no additional references are required to define the safety window of the remaining electrode voltage. Thus, the IPCC features an autonomous charge removal at controlled compensation amplitudes after each stimulus. The compensation characteristic with continuous current supply makes the IPCC suitable as a complement to monophasic stimulators, replacing their missing biphasic counter pulse. Two implementations of the IPCC were realized. Both IPCC designs are power-efficient. However, while the first IPCC implementation is fixed to a 22 V supply, the enhanced design overcomes the technological HV limitations of the employed 0.35 µm CMOS process by using a quad-rail methodology and reaches a highly adaptive power supply compliance.

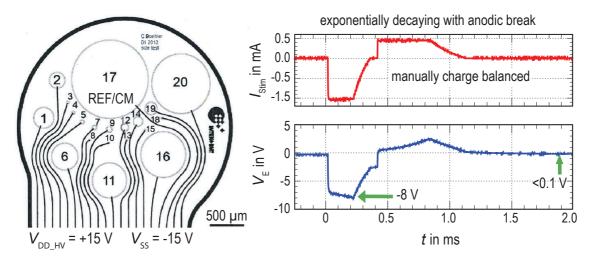

Each of the two complementary circuit solutions for cause-based and consequence-based charge compensation represents a sufficiently well performing control loop. However, providing the opportunity to achieve a better performance in charge balancing when being combined to the so called Twin-Track active charge balancer, and thus, accomplishing both: instantaneous and long-term balanced conditions. All charge balancers were characterized by simulations and verified by chip measurements via an equivalent electrical electrode model as well as in-vitro experiments.

# Zusammenfassung

Die Funktionelle Elektrostimulation von Muskel- und Nervenfasern (FES und FNS) ermöglicht es, durch künstliche Anregung mittels elektrischer Ladung, neurologische und psychische Störungen oder Erkrankungen zu behandeln. FES und FNS tragen dabei erheblich zur Steigerung der Lebensqualität beeinträchtigter Patienten bei. Exemplarisch sind hier Herzschrittmacher und Cochlea-Implantate als gut bewährte und etablierte Elektrostimulatoren zu nennen. Das Prinzip des Ladungsausgleiches ist zum wesentlichen Bestandteil der sicheren Elektrostimulation geworden, um vor Gewebeschädigung und Elektrodenkorrosion, die aufgrund einer Ansammlung verbleibender Stimulationsladungen auftreten können, zu schützen. Zu diesem Zweck werden ladungsausgeglichene, biphasische Pulsstromquellen verwendet, welche den Großteil der übermittelten Ladung durch eine Richtungsänderung während der Stimulation kompensieren. Ob es nach einem Stimulationspuls zum vollständigen Ladungsausgleich kommt, hängt jedoch von der Diskrepanz der verwendeten Bauelemente der integrierten Schaltkreise ab. Jeglicher Unterschied in Amplitude und Dauer des Stimulationspulses führt zu einer Restladung über der Elektrode, weshalb eine Ladungsausgleichsschaltung als zusätzlicher Sicherheitsaspekt unabdingbar ist. Jedoch sind gängige zertifizierte Medizinprodukte meist lediglich mit Blockkapazitäten oder passiven Methoden zum Ladungsausgleich ausgestattet, welche einen großen Flächenbedarf, eine lange Einschwingzeit sowie einen unkontrollierten Ladungsausgleich aufweisen. Eine vielversprechende Alternative für eine flächeneffiziente, schnelle und kontrollierte Ladungskompensation bietet eine aktive Ladungsausgleichregelung.

Diese Arbeit präsentiert die Forschungsaktivitäten der Autorin im Bereich der Entwicklung von CMOS-integrierten, energieeffizienten und hochspannungskompatibler, aktiver Ladungsausgleichsmethoden und -schaltungen. Darüber hinaus umfasst diese Arbeit den Beitrag der Autorin zur Entwicklung eines Hochvolt (HV)-Schalters sowie des Analogteils eines CMOS-integrierten Nervenstimulators, welcher zu Messungen mit den hier vorgestellten, aktiven Ladungsausgleichsschaltungen verwendet wurde. Moderne implantierbare Stimulatoren sind hochspezialisiert und flexibel anpassbar an die Anforderungen verschiedenster Anwendungen. Der hier vorgestellte, energieeffiziente und stromgesteuerte Stimulator ist in der Lage, frei konfigurierbare Pulsformen zu generieren und dies bei einer Hochspannungsverträglichkeit von bis zu 49 V. Der Stimulator ist mit einem passiven Ladungsausgleich durch einen neuartigen CMOS-integrierten HV-Schalter und einer aktiven Ladungsausgleichsregelung ausgestattet. Der Schwerpunkt dieser Doktorarbeit liegt auf der Entwicklung und Implementierung der aktiven Ladungsausgleichsregelsysteme.

Das erste vorgestellte Ladungsausgleichssystem basiert auf einer PI-gesteuerten Offsetkompensation und wirkt der Ursache entgegen, die für die Entstehung einer Restspannung an den Elektroden verantwortlich ist. Hierfür wird die verbleibende Elektrodenspannung nach jedem Stimulationspuls integriert und gespeichert. Die Höhe der Restspannung gilt als Maß für die Stromquellendiskrepanz. Die Amplitudenhöhe des kathodischen Strompulses des vorgestellten Stimulator-Frontends wird entsprechend angepasst und somit ein langzeitiger Ladungsausgleich erreicht. Der Regler basiert auf einem Transimpedanzverstärker, dessen Besonderheit im außerordentlich geringen Transimpedanzwert liegt und somit den Grundstein zum ersten CMOS-integrierten PI-Regler zur Offsetkompensation in neuralen Implantaten legt. Diese Arbeit umfasst eine detaillierte Stabilitätsanalyse des hier vorgestellten Regelkreises zur Anpassung verschiedener Regleroptionen an unterschiedliche Elektrodenimpedanzen.

Ein sofortiger autonomer Ladungsausgleich nach jedem unausgeglichenen Stimulationspuls wird durch ein weiteres neuartiges Konzept erreicht: die konsequenzbasierte Zwischenpuls-Ladungsregelung. Auch hier werden verbleibende Ladungen über die Restspannung an den Elektroden überwacht. Sobald Sicherheitswerte der Elektrodenspannung überschritten werden, fließt ein Kompensationsstrom. Die Methode der IPCC nutzt eine Class-B-Architektur als Kompensationsstromquelle, was den Vorteil hat, dass keine zusätzlichen Bauteile notwendig sind, um das Sicherheitsfenster der verbleibenden Elektrodenspannung zu definieren. Auf diese Weise wird eine schnelle und kontinuierliche Ladungskompensation nach jedem Stimulationspuls erzielt. Die Kompensationscharakteristik ermöglicht, mit kontinuierlicher Stromzufuhr und kontrollierbarer maximaler Amplitude, zusätzlich den Gebrauch der IPCC als Ergänzung zu einem monophasischen Stimulator, indem es dessen fehlende Gegenpulse ersetzt. In dieser Arbeit wurden zwei Implementierungen der IPCC realisiert. Beide IPCC-Schaltungen sind energieeffizient und hochspannungskompatibel. Während jedoch die erste IPCC-Implementierung auf eine 22 V-Versorgung festgelegt ist, überwindet das verbesserte Design die technologisch bedingten HV-Limitierungen des verwendeten 0,35 µm-CMOS-Prozesses mithilfe einer Vier-Schienen-Methodik. Durch die neu erzielte, anpassungsfähige Hochspannungsverträglichkeit lässt sich die IPCC-Schaltung mit Stimulatoren unterschiedlicher Versorgungsspannungen kombinieren, ohne dabei ihre charakteristische Wirksamkeit zu verlieren.

Die beiden komplementären Ansätze zur ursachen- und konsequenzbasierten Ladungskompensation stellen jeweils einen eigenständigen, leistungsfähigen Regelkreis dar. In Kombination jedoch, als sogenanntes 'Twin-Track'-System, erhöht sich die Kompensationswirksamkeit, indem sowohl ein sofortiger als auch langfristiger ausgeglichener Ladungszustand erreicht wird. Alle Schaltungen wurden in einer  $0.35\,\mu\text{m}$ -HV-CMOS-Technologie entworfen und mit Simulationen auf Transistorebene charakterisiert und anschließend durch Chipmessungen über ein äquivalentes elektrisches Elektrodenmodell sowie In-Vitro-Messungen verifiziert.

# 1. Introduction

Electrical stimulation in the medical context is the use of electricity to treat a variety of physiological diseases and disorders. After a short excursion to the history of functional electrical stimulation, this chapter motivates the topic of charge balancing as an important safety aspect of electrical stimulation.

## 1.1. Functional Electrical Stimulation

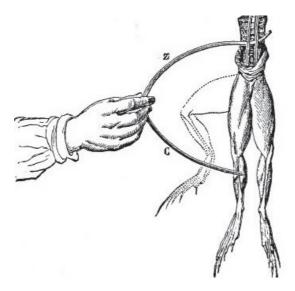

The first record for functional electrical stimulation or neural stimulation (FES/FNS) as a therapy dates back to the year 46 BC, when Scribonius Largus used currents of electric rays from torpedo fishes for the treatment of gout and chronic headaches [1]. In 1791, experiments by Luigi Galvani demonstrated induced muscle contractions of a frog's leg by placing two different metals in series to the frog's leg and its spinal cord (Fig. 1.1). He named this effect 'animal electricity', assuming that the electricity is produced by the animal itself. Two years later Volta realized that the source of electricity was the bimetallic rod and that the frog's leg serves as electrical conductor [1].

**Figure 1.1.:** Experiment of Luigi Galvani, showing muscle contractions of a frog's leg, induced by electrical discharge of a bimetallic rod (zinc (z), copper (c)). Taken from [1] (©1990, Springer).

Chapter 1 Introduction

Early in the 20<sup>th</sup> century, the nervous system was identified as the electrical conductor in animals and humans. It was demonstrated that propagation of action potentials can be triggered by applying a rapidly changing electric field near excitable tissue [2]. A first fully electrical stimulator was reported by Schmitt in 1932 [3]. Nowadays, FES is a well established treatment of a broad field of neurological or psychological diseases, in order to improve daily life quality of impaired patients by replacing physical functions previously lost or damaged. Beside cardiac pacemakers, impressive success is achieved with cochlear and retinal implants as hearing and visual prosthesis, peripheral nerve and muscle stimulators to overcome paralysis and aches, deep brain stimulation (DBS) to treat several types of neurological dysfunctions like Parkinson's disease, and vagus nerve stimulation (VNS) for blood pressure control [4–8].

## 1.2. Motivation

The motivation of this work is to find and elaborate different types of complementary metal-oxide semiconductors (CMOS) integrated circuits (IC) for active charge balancing in FES/FNS that are capable of reducing the hazards of electrical stimulation and facilitate safe chronic trials.

#### 1.2.1. Importance of Charge Balancing

FES is a technique that excites nerves by inserting electrical charge into the body. However, this may lead to residual charges in the electrode-tissue phase boundary after stimulation. Using biphasic stimulus current pulses, the main transferred charges are compensated by reversing the current direction. Nevertheless, imperfections in the fabrication process of integrated circuits are unavoidable, leading to mismatch in the biphasic waveform. Accumulated charges do not only reduce the performance of subsequent stimulations, but worse, causes electrode corrosion and tissue lesion. Therefore, in order to avoid charge accumulation, in particular during long-term treatments, charge balancing (CB) has become an integral part of FES/FNS [9]. For reliability reasons, most certified medical devices are equipped with blocking capacitors or passive charge balancing systems, despite their disadvantage in size, long settling times, and uncontrolled charge compensation. A promising approach to small, fast, and well controlled charge compensation is active charge balancing. In addition to the general requirements of active implantable systems, such as low-power consumption and low-area demand, the diversity of applications necessitates a high adaptability and flexibility of the active charge balancing system. This implies for example configurable safety limits, output current limitations and adaptive supply rails with high-voltage (HV) compatibility. All these requirements are considered and incorporated in the presented charge balancing circuit solutions.

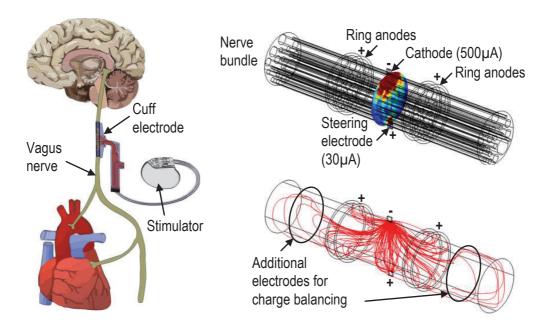

Figure 1.2.: Vagus nerve stimulation for blood pressure control by Baroloop (left) (reproduced and modified from [11] (©2009, Society for Neuroscience). Simulation of electrical field when using steering currents for an excitation of deeper nerve areas (right) (adapted from [12]). [13] (©2018, IEEE).

#### 1.2.2. Further Benefits and Applications of Charge Balancing

Beside the need for CB as a safety feature, novel research issues raise the question of compensating remaining charges not only between two stimulation pulses, but in a precisely defined, small time frame. An application example [8] arises from one of our cooperation partners Dr. rer. nat. Plachta from Neuroloop GmbH, Germany. Their promising approach to overcome chronic hypertension is selective VNS by the system BaroLoop [7]. At the event of an increased blood pressure, e.g. caused by altered stiffness of the arterial wall, the strength of the afferent nervous signals is reduced. The solution is to override the vagal signal with the help of artificial electrical stimulation. However, the transfer of blood pressure information to the brain is only one of the vagus nerve's functions. The inadvertent stimulation of non-baroreceptive fibers may cause severe side effects like bradycardia and bradypnea [8]. Therefore, BaroLoop aims to localize the relevant fibers and extract blood pressure information by tripolar recording [10] via a cuff electrode [8], which is wrapped around the vagus nerve as illustrated in Fig. 1.2 left. The localized electrode tripole is then used for selective stimulation.

The ongoing fundamental research idea of this group is to equip the stimulator setup with the capability to influence the direction of action potential (AP) propagation via steering currents. These steering currents, originating at neighboring stimulation sites, are used to either fine tune the applied current for an improved efficacy or to block the spreading of activity in unwanted directions using anodal blocks.

Chapter 1 Introduction

The principle of steering currents with  $30\,\mu\text{A}$  versus  $500\,\mu\text{A}$  stimulation currents, is illustrated in Fig. 1.2. The steering electrode is located at the opposing stimulation site in order to focus the electrical field deeper within the nerve. The distribution of the electrical field lines, as presented in the simulation results in Fig. 1.2 (right, bottom), expand even beyond the anodal rings, thus, leading to charge redistribution at neighboring sites. Therefore, it is of interest to place additional autonomous and stand-alone CB systems in some distance apart from the actual stimulation site to block the spreading of activity in unwanted directions.

Additionally, in case of inhibitory prestimulation at neighboring sites, the investigated stimulation electrode might be affected by cross-talk effects, which reduce the efficacy of the desired stimulus. Therefore, CB timed in between the inhibitory and excitatory stimulation pulses can compensate for charge imbalances caused by adjacent electrodes. It thus assists the stimulation site to regain the resting potential rapidly, resulting in an increased treatment efficacy and potentially decreased side effects. In applications with monophasic steering currents, where preprogrammed biphasic counter pulses for CB are not suitable, a charge balancer that is capable of generating counter pulses autonomously, with self-adaptive timing, is desirable.

Another application scenario with even higher challenges to the neural interface is the recording of an AP resulting from an artificial stimulus itself [14]. Such analyses will provide insights into the effects of artificial neural stimulation and the processes of neuro-modulation. For instance, in a design with DC-blocking capacitors large equalization currents hinder spinal cord potential measurement attempts [14]. For this reason, controlled and fast charge compensation is desired to bring back the electrodes that monitor the evoked AP to the body's resting potential. Since the AP signal amplitude is short and small, typically in the range of micro-volts, digital signal interference and artifacts at the sensing electrode should be avoided. Therefore, active CB in from of an analog background operation is desired and suitable to improve the signal quality during experiments with simultaneous measurement and stimulation.

In summary, CB may offer a basis for further investigations of novel research issues such as controlling the direction of AP propagation or improving the quality of simultaneous measurement and stimulation. The mentioned application examples demand a close loop balancer for an analog background operation as well as a self-adaptive balancer with automatic counter pulse generation that can be used as a stand-alone implementation. The CB solutions of this work may thus help to answer current questions and define the future roadmap for research on implantable neural interfaces.

# 1.3. Thesis Organization

This thesis is divided into nine chapters, which are organized as follows:

Chapter 1: *Introduction*. This chapter introduces electrical stimulation. Further, the idea and importance of charge balancing, which is the focus of the thesis, is motivated.

Chapter 2: Fundamentals. Although action potentials are generated physiologically, the excitation of nerves can be artificially triggered by injecting electrical charges into excitable tissue. A fundamental knowledge about anatomy and physiological excitation of nerves is required to understand how nerves can be excited technically. An insight about various charge delivery strategies, including stimulation parameters and waveforms, different electrodes and their configurations to achieve good selectivity is given. During stimulation a current transfer at the electrode-tissue interface from electron conduction in the metal to ion conduction in the electrolyte takes place. Having a closer look at this phase boundary provides a better understanding of the charge transfer processes, that lead to the equivalent electrical model of the electrode-tissue interface. The model allows to relate accumulated remaining charges to a remaining electrode voltage that is controlled and kept within a predefined safety limit by charge balancing. Thus, this chapter emphasizes the significance of charge balancing for safe electrical stimulation, since it reduces the risk of tissue damage and electrode dissolution, which might arise after unbalanced stimulation pulses.

Chapter 3: State-of-the-Art Charge Balancing. Beside the attempt to decouple DC voltages at the electrode by blocking capacitors, closed loop charge balancing systems are a promising alternative for small, fast, and controlled charge compensation. For a better overview, state-of-the-art charge balancers are classified into compensation methods that differ in their mode of action, introduced as consequence-based and cause-based charge compensation.

Chapter 4: Overall System Description and Stimulator Front-End. This chapter shows the conceptual configuration of the stimulator front-end with the proposed charge balancing circuits, which interface at the electrode. Due to the HV stimulation environment, all circuits and components must be HV compliant. Therefore, a general quad-rail methodology is presented that allows for HV compatible, power-efficient, and supply rail independent circuit designs. The section about the stimulator front-end starts with the investigation of the most beneficial current mirror topology as the basic concept of the current source design for a flexible current-controlled stimulation. The discussion is followed by the circuit implementation and measurement results with the focus on HV robustness, low-power consumption and the ability of controlled arbitrary waveform generation. Subsequently, the design and implementation of the HV compliant switch is introduced. The latter is an important interface component that separates the active charge balancing circuits from the stimulator circuitry. Additionally, the same switch architecture is

Chapter 1 Introduction

implemented for passive charge balancing, shorting the electrode via its switched on-resistance.

Chapter 5: The PI-Controlled Offset Compensation is the cause-based active charge balancing system. To monitor the low-frequency bio signals a large time constant in the milli-second range is necessary. Therefore, the PI controller was realized by a very low transimpedance amplifier, which is the heart of the circuit, and an on-chip capacitance. The design architecture and measured characteristics are presented, followed by the stability analysis of the PI-control loop. Finally, the PI-controlled Offset Compensation is compared to state-of-the-art charge balancers.

Chapter 6: The Inter-Pulse Charge Control is the consequence-based charge balancing circuit. A HV compliant amplifier monitors remaining charges and steers an advanced HV class-B push-pull stage, representing the compensating current source. Two circuit designs were implemented, both based on this novel and innovative compensation concept. The circuit designs and measurement results are presented and compared to each other, as well as to the state of the art.

Chapter 7: The Twin-Track Charge Balancer is the combination of the PI-controlled Offset Compensation and the Inter-Pulse Charge Control. The advantages of a Twin-Track charge balancer are explained and demonstrated by system measurements.

Chapter 8: Conclusion and Outlook. The last chapter concludes this work by highlighting the main achievements. A short outlook to future work is supplemented.

# 2. Fundamentals

Modern implantable stimulators have become highly specialized and adjustable to the challenges of diverse applications. In safe electrical stimulation charge balancing is a major concern, since it controls the reversion and compensation of remaining injected charges to regain the tissue's charge balanced equilibrium. Thus, reducing the risk of irreversible reactions that lead to electrode dissolution, pH change and tissue damage. This chapter¹ explains the physiological and technical nerve excitation. It gives an insight about various charge delivery strategies, stimulation waveforms, and electrode configurations to achieve good selectivity. Further, this chapter provides a closer look at the phase boundary to understand the charge transfer processes and derive an equivalent electrical model of the electrode-tissue interface. The model allows to relate accumulated charges to a remaining electrode voltage that is controlled and kept within a predefined safety limit by charge balancing.

# 2.1. Biomedical Background

The nervous system (NS) contains all neurons (nerve cells) and glia cells and can be distinguished into the central NS (CNS) and the peripheral NS (PNS). The CNS includes the brain and spinal cord, whereas the PNS is a collective term, representing the remaining parts of the NS, such as the nerves contacting muscles and organs. According to its body functions, the NS can be divided into the autonomic NS (Symphaticus and Parasymphaticus), which regulates organ functions and can hardly be influenced by will, and the somatic NS, which controls muscle functions and is influenced by will. Neurons that carry signals from sensory receptors in the PNS to the CNS are called afferent neurons. Efferent neurons, also known as motor neurons, carry signals from the CNS to the muscles or glands of the PNS [1].

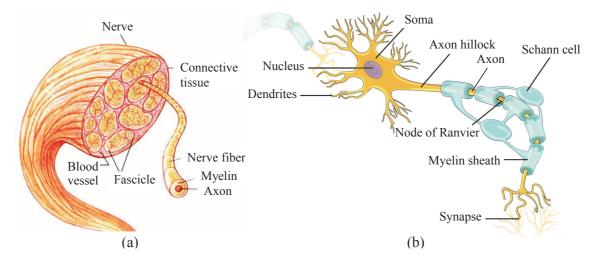

# 2.1.1. Anatomy of Nerves

In Fig. 2.1(a) the anatomy of a nerve is shown, consisting of multiple fascicles and blood vessels wrapped in a layer of connective tissue. Each fascicle is an enclosed bundle of nerve fibers. A myelinated fiber is the axon of a single neuron, covered by

<sup>&</sup>lt;sup>1</sup>The fundamentals summarized in this chapter have been partially published in a similar way in [15] by the author of this thesis.

**Figure 2.1.:** Anatomy of (a) the nerve, consisting of multiple fascicles and blood vessels wrapped in a layer of connective tissue (adapted from [16]), and (b) of the myelinated neuron (adapted from [17]).

a layer of insulation called myelin sheath. A neuron, as illustrated in Fig. 2.1(b), consists of four major components: the cell body (soma with nucleus), the receptor zones (dendrites), the conductor (axon) and its terminals (synapse). The myelin sheath of the axon is an outgrowth of the Schwann cell. It is absent at the so called nodes of Ranvier, at which transmembrane ionic transfer occurs, allowing for saltatory signal conduction. The axon carries the electrical signals from the soma to the target sites such as muscles, glands, or other neurons (dentrites). The synapses are separated from the soma of their target sites, by narrow gaps. Electrical signals that arrive at the synapse are translated into chemical signals by the release of transmitters. These transmitters travel across the synaptic gap, thereby altering the membrane potential of the target site and resulting to the post-synaptic-potential (PSP). If a sufficient excitatory PSP reaches the axon hillock of a neuron, the electrical signal in form of an actively sustained action potential (AP) is triggered.

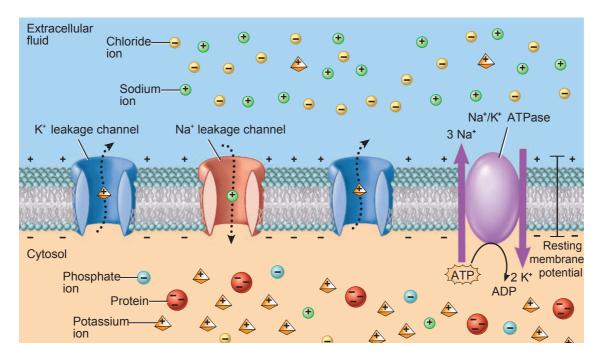

The medium inside and outside the neuron consists of water and ions. The cell membrane serves as an insulator and diffusion barrier for ions, but has certain semipermeable characteristics that allow specific ionic interchanges, see Fig. 2.2. The ionic channels in the membrane can vary their permeability in response to the transmembrane potential, allowing ions to move across the membrane down a concentration gradient. Further, ion pumps actively push ions across the membrane to establish concentration gradients across the membrane. Concentration gradients of ions across the cell membrane can be described as electrical and chemical forces. The ambition for charge equalization counteracts the ambition for concentration equalization (diffusion). In an equilibrium stage potassium  $(K^+)$  is highly concentrated in the intracellular fluid (Cytosol) and is at low concentration in the extracellular, whereas sodium  $(Na^+)$  and chloride  $(Cl^-)$  are highly concentrated in the extracellular fluid and at low concentration in the intracellular. In electrochemical equilibrium neurons

Figure 2.2.: Ionic concentration at the membrane at rest and the ionic current through the ion channels. Reproduced from [21] (©2009, John Wiley and Sons).

maintain a resting membrane potential typically around  $-60 \,\mathrm{mV}$  to  $-90 \,\mathrm{mV}$ , with the interior being negative with respect to the exterior of the cell [18–20].

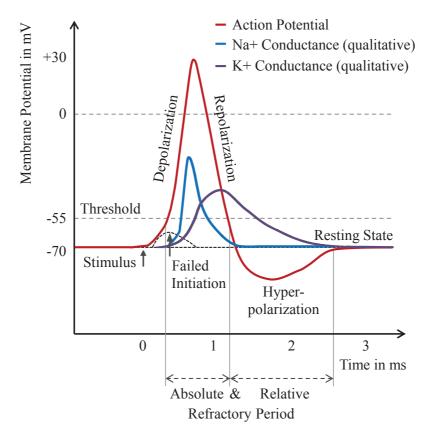

#### 2.1.2. Physiological Nerve Excitation

An AP is generated once the resting membrane potential at the axon hillock is increased beyond a threshold value by roughly 15 mV. Once the threshold is reached, the transition between resting and excited condition of the membrane occurs rather abruptly (few ms) and in a characteristic manner, as illustrated in Fig. 2.3 [18]. The first phase of the AP called depolarization, is a steep rise in potential from the resting potential to a positive potential of around 20 mV to 40 mV, under the condition that the excitation exceeds the threshold value. During repolarization, the second phase, the potential drops abruptly below the resting potential leading to the third phase, the hyperpolarization. During the absolute refractory period, a second AP cannot be initiated, independent of the strength of the applied stimulus. This interval is immediately followed by the relative refractory period in which initiation of a second AP is inhibited but not impossible. In this way refractoriness prevents backward propagation after an AP has occurred [22].

The change in charge ratio during an AP is accomplished by a delayed opening of the voltage-gated ion channels (Fig. 2.3). These channels are shut for a membrane potential that is close to the resting potential. Depolarization above threshold provokes the Na<sup>+</sup> channels to rapidly open, allowing an inward flow of Na<sup>+</sup> ions, which

**Figure 2.3.:** The phases of an action potential and the corresponding conductance of the two major ion channels. Reproduced and modified from [23].

produces a further rise in membrane potential (depolarization). By reversion of the membrane potential, the Na<sup>+</sup> channels close and the permeability for Na<sup>+</sup> decreases again. Almost simultaneously with the opening of the Na<sup>+</sup> channels the K<sup>+</sup> channels slowly start to open. As these channels exhibit inertia, the permeability of K<sup>+</sup> ions is still increasing, while the Na<sup>+</sup> channels are already closed, thus, returning the electrochemical gradient to the resting state (repolarization). The inert behavior of K<sup>+</sup> channels cause additional K<sup>+</sup> currents after the resting potential is reached, leading to hyperpolarization. After an AP has occurred the ionic distribution of the resting potential is reestablished by the Na-K-Pump under the consumption of metabolic energy Adenosine Triphosphate (ATP) [22].

In unmyelinated nerve fibers, voltage-gated ion channels are located all over the membrane. Thus each membrane area, along the full length of the axon, needs to be excited consecutively for AP propagation. The AP spreads along the axon, depolarizing adjacent region of the axon. This type of propagation depends on a number of factors, for example the cross-sectional width of the axon. For nerve fibers of class C according to Erlanger/Gasser, the propagation velocity is typically around 1 m/s at a mean fiber diameter of 1  $\mu$ m [24]. Although increasing the diameter leads to an increased velocity, unmyelinated conduction is rather slow and not suited for

higher speed requirements. A faster and more efficient conduction is promoted by myelinated fibers. Myelin sheaths of up to 2 mm long sections are wrapped around the axon, efficiently insulating it [25]. Voltage-gated ion channels are only located at the nodes of Ranvier. The AP propagates along the myelinated axon by jumping from one node of Ranvier to the next (saltatory conduction). It therefore propagates faster along the axon as it would in the absence of myelin. The conduction velocity is increased without the need to increase the axon's diameter. For nerve fibers of class A according to Erlanger/Gasser, the propagation velocity can go up to 120 m/s at a mean fiber diameter of around 15 µm [24]. An important property of action potential propagation is the all-or-none law, which holds for both conduction types. It reveals that if the stimulus is above threshold, the nerve will give a complete response. Otherwise no response at all will be generated. An AP is then propagating without decreasing its amplitude over the entire length of the nerve fiber. The depolarized regions are the stimulus for adjacent regions [22].

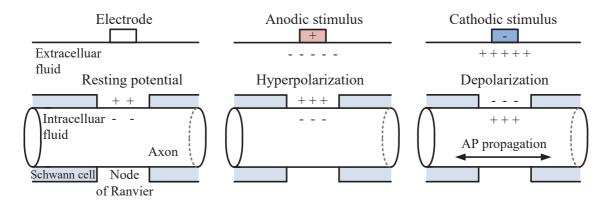

#### 2.2. Technical Nerve Excitation

Electrical stimulation of nerves is the technically triggered excitation of a neuron by artificially depolarizing the axon's membrane. Technical systems interface nerves via electrodes, which are placed in direct contact with the excitable tissue. During stimulation a current transfer from electron conduction in the solid state of the electrical circuit to ion conduction in the fluid state of the electrolyte takes place, leading to a potential difference between the extracellular and intracellular fluid of the neuron at the electrode site. In Fig. 2.4 the effect on the membrane's potential of an axon is shown for a positively charged electrode during an anodic stimulus, and a negatively charged electrode during a cathodic stimulus. A positively charged electrode leads to hyperpolarization, whereas the negatively charged electrode triggers APs at adjacent nodes of Ranvier in both directions, presupposed that the potential difference exceeds the threshold value.

**Figure 2.4.:** The effect of electrode polarization during technical nerve excitation.

## 2.2.1. Charge Delivery Strategies

There are basically three different methods to polarize the electrode: voltage, charge, and current mode stimulation [6]. They are physically linked but describe different approaches for charge delivery, i.e. controlled by a voltage source, capacitive discharge, or a current source. Voltage controlled stimulation suggests itself, since the electrical excitation is dependent on the voltage applied across the neuron's membrane. However, it is the charge that has to be controlled, since the metal-electrolyte interface is characterized by a maximum allowed charge that can be transferred from the electrode into the biological tissue. Additionally, taking into account that the load impedance varies over time, the injected charge differs when using voltagecontrolled stimulators, which is why they are rarely used in modern implantable systems [4, 5]. Using charge-controlled stimulation via capacitive discharge, the stimulation charge is accurately controlled [6, 26–28]. However, in case of high load capacitances, large discharge capacitors are required for sufficient charge delivery, which is a disadvantage for implantable micro systems. Furthermore, the waveform of the applied charge is predefined by the discharge characteristic and offers little flexibility. Current-controlled stimulation, in which pulse width  $t_{\rm w}$  and stimulus current amplitude  $I_{\text{Stim}}$  is controlled regardless of impedance variations, are most commonly used [4, 5, 29], as charge and current are directly linked by

$$Q = \int_0^{t_{\rm w}} i(t)dt = I_{\rm Stim} \cdot t_{\rm w}, \qquad (2.1)$$

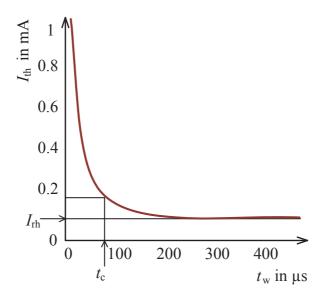

when rectangular stimulation is applied. Nevertheless, when using current-controlled stimulation it has to be considered that for high load impedances, high voltages are required to accommodate a certain level of current, requiring HV CMOS processes for application specific IC (ASIC) development. Therefore, beside current-controlled stimulators at low-voltage (LV) supplies with a maximum compliance of 3 V to 5 V [6, 30–32], HV compliant stimulators in the range of 20 V to 36 V have been published in [4, 5, 33–36]. For each application, the relationship between amplitude and pulse width for a successful stimulation can be experimentally derived by the strength-duration curve [2]. A strength-duration curve is exemplarily shown in Fig. 2.5. The amplitude of the threshold current  $I_{\rm th}$ , required to rise the membrane potential above threshold, decreases with increasing pulse width  $t_{\rm w}$  until a minimum current amplitude, the rheobase current  $I_{\rm rh}$ , is reached. The minimum  $t_{\rm w}$ , that is needed for nerve excitation, with a current amplitude of twice  $I_{\rm rh}$ , is called chronaxie time  $t_{\rm c}$ . Both values are useful to describe the electro sensitivity of the target tissue [2, 37].

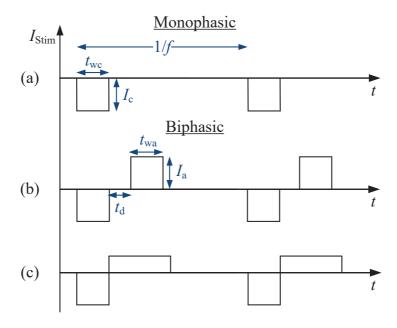

Different current waveform shapes like square, sinusoidal, ramp, or exponential are possible for successful stimulation and their efficiency and effect of parameters are analyzed by [38, 39]. However, the shape of waveform is irrelevant for the success of charge balancing. Since the focus lies on charge balancing, only monophasic and biphasic rectangular pulses, as shown in Fig. 2.6, are considered in this work. Monophasic stimulation consists of a negative (cathodic) stimulation pulse, illustrated in Fig. 2.6(a), that depolarizes the nerve, and thereby, evokes the desired

Figure 2.5.: Strength-duration curve. Reproduced from [2].

Figure 2.6.: Rectangular stimulation waveforms, (a) monophasic stimulus, (b) symmetric rectangular biphasic waveform with cathodic-first current and pulse delay, and (c) asymmetric biphasic waveform with cathodic-first current.

physiological effect. The characteristic parameters are cathodic amplitude  $I_c$ , cathodic pulse width  $t_{wc}$ , and stimulation frequency f. The more commonly used biphasic stimulation waveform, illustrated in Fig. 2.6(b) and (c), consists of a cathodic stimulating phase and an anodic counter phase, reversing the electrochemical reactions by a pulse of opposite sign [40]. Beside the cathodic parameters and stim-

ulation frequency, the biphasic waveform is characterized by anodic amplitude  $I_{\rm a}$ , pulse width  $t_{\rm wa}$ , as well as a possible delay time  $t_{\rm d}$  between the two phases. Typical values for FES given by [41] are current amplitudes  $I_{\rm a,c}$  of 1 mA, pulse widths  $t_{\rm w}$  of up to 500 µs, and stimulation frequency f of 10 Hz to 30 Hz. A perfectly balanced stimulus provides equal amount of positive and negative charges, however,  $I_{\rm a,c}$  and  $t_{\rm wa,wc}$  can be chosen identical (Fig. 2.6(b)), or asymmetric (Fig. 2.6(c)). Biphasic waveforms with cathodic-first current are usually favored, since the anodic pulse hyperpolarizes the nerve and elevates the excitation threshold [42].

#### 2.2.2. Electrodes

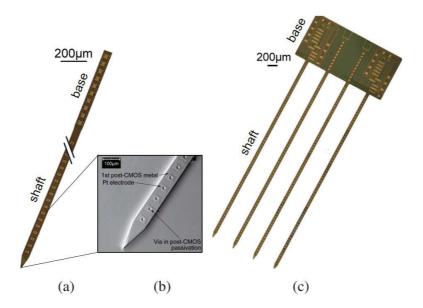

For chronic implantation, long term biostability of the electrodes with minimal corrosion must be provided for several decades. Commonly used materials for stimulation electrode contacts are non-noble metals like stainless steel 316 or nickel-cobalt alloys, as well as noble metals, such as platinum and iridium oxide. Noble metals are preferred for electrical stimulation due to their smaller corrosion rates. However, corrosion still takes place during electrical stimulation and can be observed by weight loss, dissolution of metal ions and deposition of the ions in the surrounding tissue. Corrosion does not only result in deterioration and destruction of the electrode material, but also in tissue damage [43]. Thin film electrodes are manufactured by means of microsystem technologies and clean room processes. Different designs of multichannel electrode arrays offer a preselection of the working electrode, to stimulate a certain envisioned site of the nerve. The shaft array, shown in Fig. 2.7, belongs to a kind of intraneural electrodes, also referred to as intrafascicular electrodes that are placed directly inside the nerve by penetrating the tissue. The close proximity to the target site allows good stimulation selectivity. However, penetrating the nerve during implantation can lead to significant nerve damage.

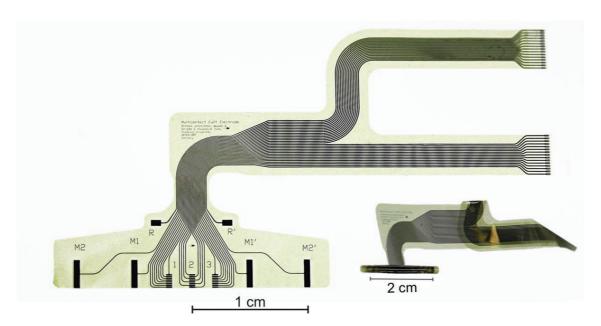

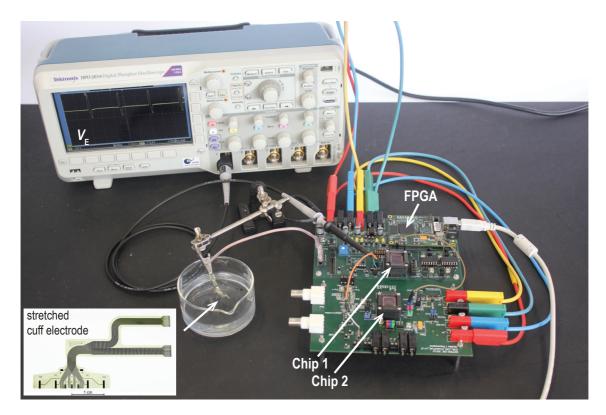

The spiral multichannel cuff electrode, shown in Fig. 2.8, represents an extraneural electrode array that interfaces the nerve by surrounding its surface without penetrating nervous tissue [2]. The anatomical structure of the nerve remains intact during and after implantation. Compared to intraneural electrode concepts, the advantage of less invasiveness and self-sizing properties is accompanied by some disadvantages, such as an increased current threshold to excite nerve fibers. The high number of electrode sites on the inner perimeter of the cuff allows selective stimulation of different parts of the nerve on the fascicular level. However, the ability to selectively stimulate different nerve fibers is limited, since only bundles of fibers can be stimulated simultaneously. A cuff electrode, like the one shown in Fig. 2.8, provided by neuroloop GmbH, Freiburg, Germany, is used for system verification in this thesis. The cuff is manufactured as a planar sheet, then tempered to roll and shape it into a three-dimensional structure. For the thin film metallization layer, 300 nm platinum is sputtered and coated with 1000 nm iridium oxide. Polyimide is used as substrate and insulation material. The cuff features 24 working electrodes, arranged in three rows of eight electrodes each, and four adjacent outer ring electrodes, all facing inside the cuff. Two electrodes facing outside are provided as reference electrodes. The cuff's total length is 20 mm and the inner diameter is 0.8 mm [7, 8, 44].

Figure 2.7.: Micrograph of neural electrode shaft arrays. (a) Slim shaft. (b) Scanning electron microscopy micrograph of the tip section. (c) Combination of multiple shafts into a comb structure. Modified from [45] (©2018, IEEE).

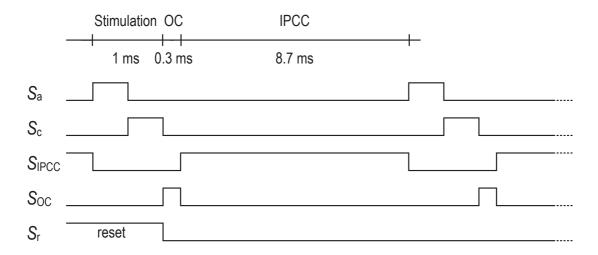

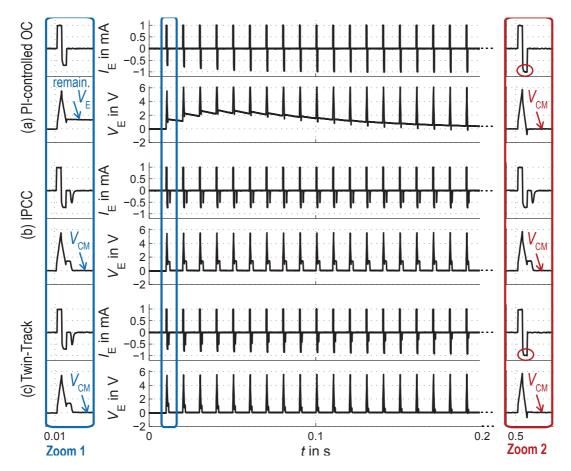

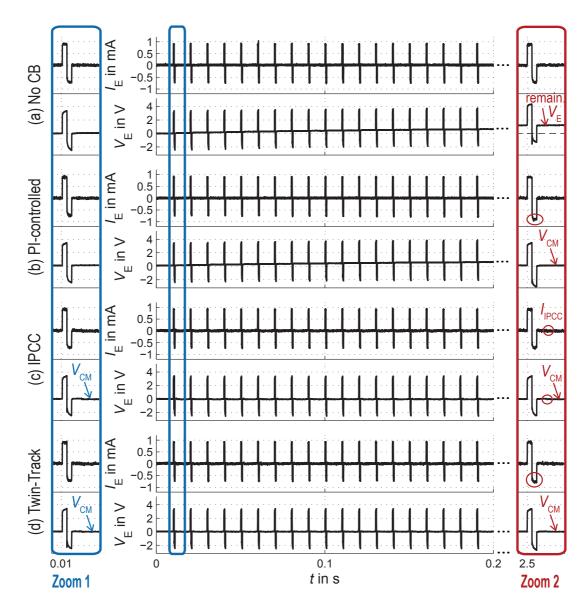

Figure 2.8.: Photograph of the polyimide thin film cuff electrode. Large image: after micromachining with eight electrodes arranged in tripoles in the middle (1, 2, 3), four outer ring electrodes (M1, M1', M2, M2'), and two reference electrodes (R, R'). Small image: spiral cuff in its wrapped condition. Modified from [8, 44].

## 2.2.3. Selectivity

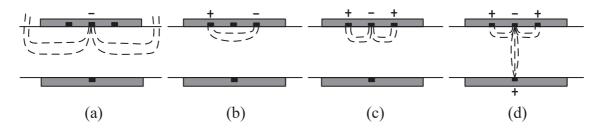

The selectivity of a target tissue or selected nerve fiber can be improved by the choice of an appropriate electrode configuration and stimulation technique. At least two electrodes are necessary to provide a current flow for electrical stimulation, the working electrode and a counter electrode. In case of monopolar stimulation (Fig. 2.9(a)), the electrons arrive on the working electrode with a relatively small surface area. The counter electrode has a larger surface area and can be located within quite a distance. It is basically the ground electrode, which exhibits the body's quiescent potential. The current is focused near the electrode and tends to enter the insulation material of the electrode array at its ends in a uniform way. Bipolar stimulation (Fig. 2.9(b)) is similar to monopolar stimulation, but the counter electrode is located on the electrode array and is of opposing polarity. The position and size of the counter electrode defines the shape of the electrical field. Another possible electrode configuration is tripolar configuration (Fig. 2.9(c)), where two adjacent electrodes are used as counter electrodes with opposing polarity [34, 39]. The current will flow from the counter electrodes to the central working electrode. This configuration has advantages concerning the ability of defining and focusing the superficial excitation sites of a nerve [46]. In order to restrict the excitation to deeper nerve areas and block non-requested superficial fibers, transverse steering currents can be applied by a multipolar electrode configuration, as shown in Fig. 2.9(d) [46].

Figure 2.9.: Electrode configuration for, (a) monopolar, (b) bipolar, (c) tripolar, and (d) multipolar stimulation using steering currents. Reproduced and modified from [46] (©1990, IEEE).

#### 2.3. Electrode-Tissue Interface

Electrodes represent the interface between stimulator circuit and excitable tissue. During stimulation a current transfer at the phase boundary from electron conduction in the solid state (metal) to ion conduction in the fluid state (electrolyte) takes place. According to the charge transfer mechanisms at the phase boundary, the equivalent electrical model of the electrode-tissue interface is derived.

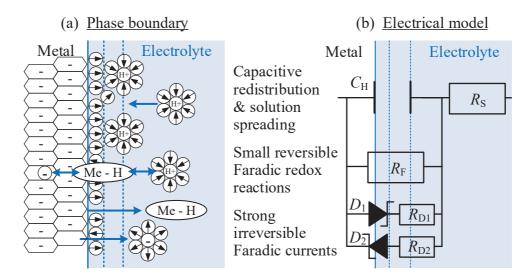

#### 2.3.1. Charge Transfer at the Phase Boundary

The two main charge transfer mechanisms at the phase boundary of the electrodetissue interface are: capacitive charge redistribution, and Faradic reactions, illustrated in Fig. 2.10(a). In contrast to Faradic reactions, the charge transfer via capacitive mechanism happens without any crossing or exchange of charge carriers at the phase boundary. Carriers of opposing polarity, electrons in metal and hydrated protons in electrolyte, accumulate at the phase boundary, separated by a dielectric layer of water. The capacitive arrangement of these layers is known as the Helmholtz double layer. Charging and discharging of the Helmholtz double layer is completely reversible, the charge transfer takes place without any electrochemical reactions nor electrode or tissue damage. Therefore, the capacitive charge redistribution is the preferred charge transfer mechanism for successful and safe stimulation. The capacitive mechanism dominates at a small voltage across the phase boundary for a small amount of charge. The charge density capacity of a smooth surface metal electrode is up to  $20\,\mu\text{C/cm}^2$ . If the injected or withdrawn charge exceeds this density limit, the excess charge is transferred by Faraday currents [43]. Thereby, charge carriers cross the phase boundary, leading to reduction and oxidation (redox) reactions. Reduction, the addition of electrons, occurs at a negatively charged electrode (cathode), while oxidation, the removal of electrons, takes place at a positively charged electrode (anode).

One can distinguish between reversible and irreversible Faradic reactions. Reversible reactions are stationary, thus, the reactants stay near the electrode surface. Reversible mechanisms include oxide formation or reduction and hydrogen plating at platinum or other noble metals like iridium [43]

$$Pt + H_2O \longleftrightarrow PtO + 2 \cdot H^+ + 2 \cdot e^-,$$

(2.2)

$$Ir + 2 \cdot H_2O \longleftrightarrow Ir(OH)_2 + 2 \cdot H^+ + 2 \cdot e^-.$$

(2.3)

The surface redox reactions might change the oxidation state of the metal oxide, however, they do not create new chemical species in the biological tissue and are reversed by changing the polarity of the applied stimulus. The overall chemical composition remains unchanged, and therefore, the reversible Faradic reactions are considered as physically harmless [2, 43].

Figure 2.10.: The phase boundary of the electrode-tissue interface describing (a) the charge transfer mechanisms and reactions (reproduced and modified from [43]), and (b) the equivalent electrical model.

Irreversible Faradic redox reactions arise in case of larger permanent currents or voltages across the electrode-tissue interface. In this case, the mass transport rate dominates the electron transport rate in the electrolyte, and the resultant reaction products diffuse into the solution (Fig. 2.10). Irreversible mechanisms include also electrode corrosion

$$Pt + 4 \cdot Cl^{-} \longrightarrow [PtCl_{4}]^{2-} + 2 \cdot e^{-} \tag{2.4}$$

and electrolysis of water, leading to hydrogen or oxygen evolution

$$2 \cdot H_2 O + 2 \cdot e^- \longrightarrow H_2 \uparrow + 2 \cdot OH^-, \qquad (2.5)$$

$$2 \cdot H_2O \longrightarrow O_2 \uparrow + 4 \cdot H^+ + 4 \cdot e^-, \tag{2.6}$$

where the symbol  $(\uparrow)$  indicates gas evolution. These reactions alter the composition of the electrode surface and generate toxic reaction products with pH change of the surrounding solution. In summary, irreversible Faradic reaction are unwanted charge injection processes and must be circumvented during electrical stimulation, since they cause damage to both, the electrode and the tissue [2, 43].

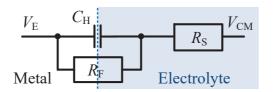

# 2.3.2. Equivalent Electrical Model

Based on the charge transfer mechanisms at the phase boundary, an equivalent electrical model of different types of electrical components can be derived, as shown in Fig. 2.10(b). The charge accumulation at the phase boundary that forms the

Figure 2.11.: Simplified equivalent electrical model of the phase boundary.

Helmholtz double layer and builds up a potential difference, exhibits the behavior of a parallel plate capacitor. The parallel plate capacitance

$$C_H = \varepsilon_0 \cdot \varepsilon_r \cdot \frac{a}{d_H},$$

(2.7)

with electric constant  $\varepsilon_0$ , relative permittivity of electrolyte  $\varepsilon_r$ , and  $d_H$  the thickness of the Helmholtz double layer, depends mainly on the electrode surface area a [43]. Additionally, the electron conduction in metal is transferred into ion conduction in electrolyte, the latter is modeled by the solution spreading resistance  $R_S$  in series to  $C_H$ . Further, a resistance  $R_F$  is introduced in parallel to  $C_H$ , representing reversible Faradic currents. The technical implementation for strong Faradic currents is the parallel connection of two Zener diodes  $D_1$  and  $D_2$ , modeling irreversible positive and negative currents, respectively. More complex model descriptions, e.g. considering diffusion of the chemical reactants in solution by the Warburg impedance, can be found in [43]. However, for safe stimulation, which implies that the voltage across the tissue interface is kept low and strong Faradic currents are prevented, the electrodetissue interface is simplified to the model shown in Fig. 2.11. Its complex impedance Z, with respect to the stimulation frequency  $\omega$

$$Z(\omega) = \left(\frac{1}{R_{\rm F}} + jwC_{\rm H}\right)^{-1} + R_{\rm S},$$

(2.8)

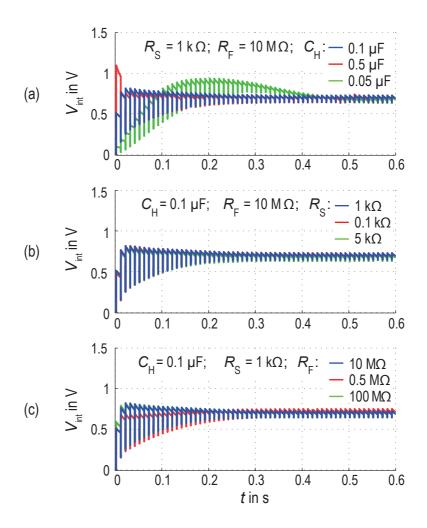

describes the current-voltage behavior at the electrode as a first order high pass. The electrode values vary depending on the material and geometry [9]. The equivalent model parameters of a cuff electrode and given values from literature are listed in Tab. 2.1. The equivalent model parameters of the cuff electrode are extracted from data of an impedance measurement over a frequency sweep, using the fitting tool of the software program MATLAB for Eq. (2.8). However, uncertainties about the extracted impedance values are still an issue due to tissue growth and electrode migration after surgery [47].

# 2.3.3. Remaining Charges and Safety Limits

The charge density, which is the total charge divided by the area of  $C_{\rm H}$ , must be kept below a critical charge limit to ensure save charge injection during stimulation. The reversible charge injection limit, also referred to as water window, depends mainly

| Table 2.1.: | Parameters | of the | equivalent | electrical | model | for | different | types | of |

|-------------|------------|--------|------------|------------|-------|-----|-----------|-------|----|

| electrodes. |            |        |            |            |       |     |           |       |    |

| type                           | cuff <sup>*</sup><br>[7, 8] |                    |                | retinal [4] |       |       | retinal [48] | wire<br>[49]  |

|--------------------------------|-----------------------------|--------------------|----------------|-------------|-------|-------|--------------|---------------|

| material                       | Pt coated with IrO2         |                    |                | Pt black    |       |       | IrO2         | Pt-Ir         |

| size in mm <sup>2</sup>        | 0.075<br>working            | 0.425<br>reference | 1.225<br>anode | 0.002       | 0.031 | 0.785 | -            | 'tip<br>area' |

| $C_{\rm H}$ in $\mu {\rm F}$   | 0.5                         | 7                  | 20             | 0.022       | 0.11  | 5.5   | 1.1          | 0.2           |

| $R_{\rm S}$ in ${\rm k}\Omega$ | 3                           | 1.5                | 1.0            | 8.72        | 3.46  | 1.15  | 1.1          | 10            |

| $R_{\rm F}$ in ${\rm k}\Omega$ | 150                         | 20                 | 15             | -           | -     | -     | >10 000      | 500           |

<sup>\*</sup> extracted from measurements

on the material of the electrode and can be defined during cyclic voltammetry [43]. The water window of platinum electrodes, for example, lies between  $-600\,\mathrm{mV}$  and  $800\,\mathrm{mV}$  [50]. Therefore, safe electrical stimulation considers stimulation parameters that keep the charge density of each stimulus within the water window for the chosen electrode type. However, application-specific stimulation parameters are only one part of the solution for safe stimulation. Additionally, ideal safe electrical stimulation requires zero residual charges across the electrode-tissue interface to avoid the transfer of net charge that might lead to irreversible Faradic reactions.

Residual charges are related to the remaining electrode voltage  $V_{\rm E}$  across the electrode-tissue interface with respect to the body's quiescent potential  $V_{\rm CM}$ . The development of residual charges is shown at an example of a monophasic rectangular stimulus with intensity  $I_0$  and pulse width  $t_{\rm w}$ , and its corresponding voltage waveform in Fig. 2.12. The generated voltage at any time  $t < t_{\rm w}$  is mathematically described by

$$V_{\rm E}(t) = I_0 \cdot R_{\rm s} + I_0 \cdot R_{\rm F} \cdot (1 - e^{\frac{-t}{R_{\rm F}C_{\rm H}}}), \ t_0 \le t < t_{\rm w},$$

(2.9)

where the initial voltage increment equals the voltage drop across  $R_{\rm S}$  due to the steep transient increase of  $I_0$ . The second term results from  $I_0$  gradually charging  $C_{\rm H}$ . Ideally, for  $R_{\rm F}$  towards infinity, this part exhibits ideal integration

$$V_{\text{E,int}} = I_0/C_{\text{H}} \cdot t_{\text{w}}, \qquad (2.10)$$

with linear voltage increase during  $t_{\rm w}$ . However, for a finite value of  $R_{\rm F}$ , Faradic current through  $R_{\rm F}$  conducts a portion of the injected current  $I_0$ , causing a nonlinear voltage increment, which approaches  $I_0R_{\rm F}$ , with time constant  $R_{\rm F}C_{\rm H}$ . The abrupt stop of  $I_0$  through  $R_{\rm S}$  at the end of the stimulus results in a sudden voltage drop. The resultant  $V_{\rm E}$  then corresponds to the charge stored in  $C_{\rm H}$  and diminishes only

Figure 2.12.: The corresponding voltage waveform for a monophasic rectangular current pulse across the equivalent electrical model.

slowly with time

$$V_{\rm E}(t) = \left(I_0 \cdot R_{\rm F} \cdot (1 - e^{\frac{-t_{\rm w}}{R_{\rm F}C_{\rm H}}})\right) \cdot e^{\frac{-t}{R_{\rm F}C_{\rm H}}}, \ t \ge t_{\rm w},$$

(2.11)

by passive discharge through the resistive path. [50, 51]

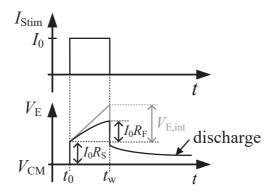

A common approach to avoid large remaining voltages is to use biphasic stimulation pulses instead of a monophasic pulse. An ideal biphasic stimulation provides equal amount of cathodic and anodic charges. After each stimulus,  $V_{\rm E}$  safely returns and stays at the reference potential  $V_{\rm CM}$ , as shown in Fig. 2.13(a). However, in reality, mismatch between the cathodic and anodic charge packages, illustrated by  $\Delta Q$  in Fig. 2.13(c), inevitably occurs due to process variations. Moreover, [50] emphasizes that even with matched biphasic current pulses a residual voltage  $V_{\rm E}$  exists, due to leakage current via  $R_{\rm F}$  if the delay time  $t_{\rm d}$  is not zero (Fig. 2.13(c)). Including the effect of a non zero  $t_{\rm d}$  and assuming a mismatch in the biphasic waveform leads to a residual voltage  $V_{\rm E}$  of

$$V_{\rm E} = \left( -I_{\rm c} \cdot R_{\rm F} \cdot \left( 1 - e^{\frac{-t_{\rm wc}}{R_{\rm F}C_{\rm H}}} \right) \cdot e^{\frac{-t_{\rm d}}{R_{\rm F}C_{\rm H}}} + I_{\rm a} \cdot R_{\rm F} \cdot \left( 1 - e^{\frac{-t_{\rm wa}}{R_{\rm F}C_{\rm H}}} \right) \right) \cdot e^{\frac{-t_{\rm dis}}{R_{\rm F}C_{\rm H}}}, \quad (2.12)$$

at the end of one stimulation cycle. Usually,  $t_{\rm d}$  is short and  $R_{\rm F}$  large, which diminishes its effect on the residual voltage  $V_{\rm E}$  compared to a mismatch in stimulation amplitude  $I_{\rm a}$  and  $I_{\rm c}$  or pulse width  $t_{\rm wa}$  and  $t_{\rm wc}$ . During  $t_{\rm dis}$ ,  $C_{\rm H}$  discharges passively through  $R_{\rm F}$ . However, a complete discharge is only possible, if  $t_{\rm dis}$  is sufficiently long

$$t_{\rm dis} \gg \tau_{\rm dis} = R_{\rm F} \cdot C_{\rm H} \,.$$

(2.13)

Otherwise, an offset potential at the beginning of a subsequent stimulus exists. Charge accumulation of further stimulation cycles intensifies the problem. Without compensating the excess charges, a dangerous voltage level will be reached, leading to irreversible Faradic reactions. Therefore, predefined safety limits of  $\pm 50 \,\text{mV}$  [6] or  $\pm 100 \,\text{mV}$  [4, 9], well below the water window, are considered around the neurons' quiescent potential  $V_{\text{CM}}$ , within which  $V_{\text{E}}$  is tolerable.

Figure 2.13.: Comparison between (a) ideal biphasic stimulation, (b) biphasic stimulation including delay time  $t_{\rm d}$ , and (c) real biphasic stimulation with current mismatch  $\Delta Q$  leading to dangerous remaining electrode voltages.

# 2.4. Summary

Although APs are generated physiologically, the excitation of nerves can be artificially triggered by injecting electrical charges into excitable tissue, and thus, changing the transmembrane resting potential. Different charge delivery strategies are discussed in this chapter. Among these, the current-controlled stimulation is favored, since it allows for a good control of the transferred charge, regardless of impedance variations. Electrodes represent the interface between stimulator circuit and biological tissue. Different types of electrodes are exemplarily introduced. Further, it is explained how an appropriate configuration of the active electrodes of an electrode array, increases the spatial selectivity for the excitation of the selected fiber within a nerve.

A first approach for tissue and electrode protection is using biphasic stimulation pulses that ideally reverse all electrochemical reactions at the phase boundary. However, any monophasic or unbalanced biphasic stimulus causes residual net charges across the electrode-tissue interface, leading to irreversible Faradaic reactions with toxic byproducts causing pH changes and electrode dissolution. Therefore, any residual charge must be monitored and controlled. A measure for the residual charge is the remaining electrode voltage  $V_{\rm E}$ . With respect to the application and electrode material safety limits are defined, in which  $V_{\rm E}$  is tolerable. At this point charge balancing becomes indispensable, as it keeps  $V_{\rm E}$  within these predefined safety limits. An equivalent electrical model of the electrode-tissue interface is derived by having a closer look at the charge transfer mechanisms of the phase boundary. The model is simplified to three main components, which are the Helmholtz double-layer capacitor  $C_{\rm H}$ , a solution spreading resistance  $R_{\rm S}$ , and the Faradaic resistance  $R_{\rm F}$ .

# 3. State-of-the-Art Charge Balancing

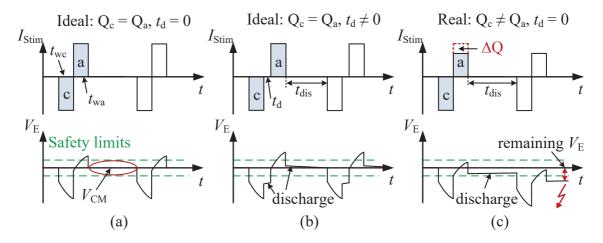

Safety in neural electrical stimulation is a major theme addressed by nowadays scientists. There exist different approaches for electrode and tissue protection, which ensure that no net charge is transferred at the electrode-electrolyte interface. This chapter summarizes state-of-the-art charge balancing methods. An overview about the different charge balancing categories is given in Fig. 3.1. Beside the attempt to decouple DC voltages at the electrode by blocking capacitors, closed loop charge balancing systems compensate residual charges by comparing the remaining electrode voltage  $V_{\rm E}$  to the body's quiescent potential  $V_{\rm CM}$ . In the group of closed loop charge balancing, we distinguish between two compensation methods that differ in their mode of action. The consequence-based approach aims for an instantaneous reduction of  $V_{\rm E}$  above the safety limit, after each stimulus. The cause-based methods counteract mismatch and process variations and ensure a long-term balanced condition, for example, by adjusting the charges of the anodic and cathodic stimulus, typically averaged over many pulses. After a general introduction of previous methods, the thesis concentrates on the methods marked in red. A detailed description about their principles, designs and measurement results are given in the subsequent chapters.

Figure 3.1.: Overview of state-of-the-art charge balancing categories.

# 3.1. Blocking Capacitors

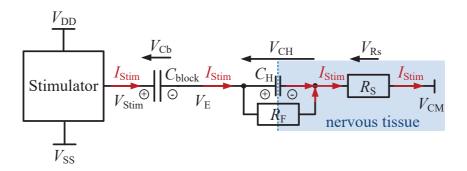

Introducing a blocking capacitor  $C_{\rm block}$  in series to the electrode, as illustrated in Fig. 3.2, is often argued [40, 52, 53] to protect the tissue against net currents. Maximum allowed net currents are defined in [54], being determined by observing tissue damage and relating it to an overall net current, calculated by current integration over time. However, the influence of the electrode impedance, e.g. the amount of charge accumulation and the capability of self-discharge, is neglected. Therefore, the derived current limits are not universally valid, on the contrary, they vary considerably from one application to another.

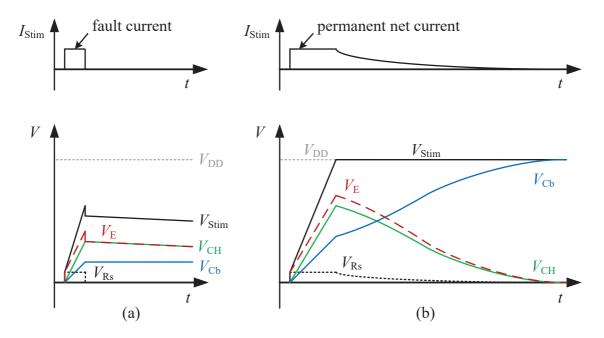

Having a closer look at the effectiveness of a blocking capacitor by considering voltage and current mode stimulation makes clear that it is not a sufficient protection method. In the case of voltage mode stimulation,  $C_{\rm block}$  isolates  $V_{\rm E}$  from the DC level of  $V_{\rm Stim}$  on the circuitry side. Thus, a self-discharge at the electrode via  $R_{\rm F}$  can take place until  $V_{\rm E}$  equals  $V_{\rm CM}$ . Nevertheless, fast switching events and AC voltages (like stimulation pulses) will pass  $C_{\rm block}$  and may lead to an unwanted residual voltage  $V_{\rm CH}$  across the Helmholtz capacitor  $C_{\rm H}$ . Considering current mode stimulation, any AC currents and erroneous DC offset currents are being integrated not only at  $C_{\rm block}$  but also at  $C_{\rm H}$ , thereby mobilizing ions in the tissue that accumulate at the phase boundary, as illustrated in Fig. 3.2. Therefore, introducing a blocking capacitance will not protect the electrode from the development of a residual voltage  $V_{\rm CH}$ , as it is demonstrated in Fig. 3.3(a). Only in case of a permanent net current, shown in Fig. 3.3(b), that causes  $V_{\rm Stim}$  to reach a constant voltage level, e.g. the supply  $V_{\rm DD}$ , blocking capacitors are reasonable since they interrupt the integration process at  $C_{\rm H}$  and allow for a complete self-discharge of  $V_{\rm CH}$ .

Furthermore, an additional voltage drop across  $C_{\rm block}$ ,  $V_{\rm Cb}$  illustared in Fig. 3.2, is induced during stimulation, and increases the voltage overhead of  $V_{\rm Stim}$  required for successful stimulation. Therefore,  $C_{\rm block}$  must be chosen significantly larger than  $C_{\rm H}$  to result in a voltage drop that is negligible small compared to the one across  $C_{\rm H}$

**Figure 3.2.:** Schematic of the system setup with a blocking capacitor  $C_{\text{block}}$  at the output of the stimulator, illustrating the additional voltage drop  $V_{\text{Cb}}$  that is induced within the signal path.

Figure 3.3.: Schematic signal diagram, describing in (a) the irrelevance of  $C_{\text{block}}$  in case of fault AC or DC currents, and in (b) the positive effect of  $C_{\text{block}}$  on the electrode voltage  $V_{\text{E}}$  for net currents once  $V_{\text{Stim}}$  stays constant, i.e. due to clipping.

[40]. Blocking capacitances are expected in the range of  $1\,\mu\text{F}$  to  $100\,\mu\text{F}$  and have to be realized off-chip bringing along disadvantages in terms of area and assembly. Additionally, a regular discharge of  $C_{\text{block}}$  is necessary to avoid voltage saturation.

Even though, using blocking capacitors is an accepted method, and practiced in many certified medical devices, it can be stated that  $C_{\rm block}$  has disadvantages in terms of area and effectiveness. It is neither a sufficient protection nor an alternative to CB in current mode stimulators.

# 3.2. Consequence-Based Charge Balancing Methods

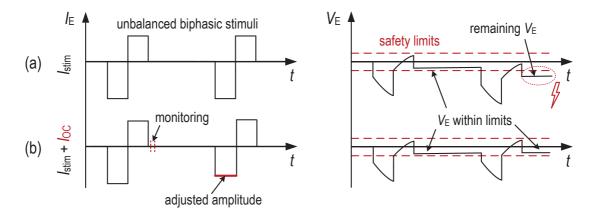

The consequence-based compensation methods aim for an instantaneous discharge of the remaining electrode potential by inserting additional charges of opposite polarity to the electrode or allow for an electrode self-discharge. The imbalance in the stimulus itself stays untouched. Therefore, once accumulated charges at the electrode become critical, compensation after each stimulus is required continuously.

**Figure 3.4.:** Passive charge balancing by shorting the electrode via a discharge resistor or a similar discharging circuit. Taken from [9] (©2010, IEEE).

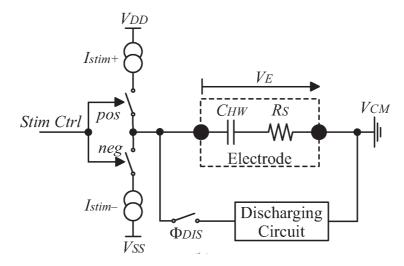

#### 3.2.1. Passive Charge Balancing

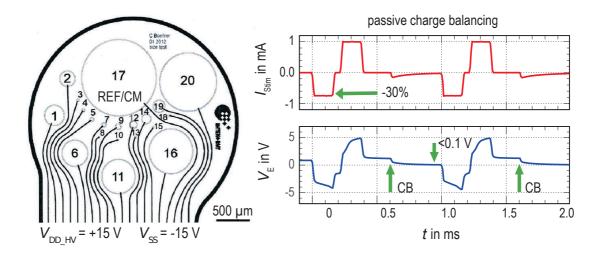

One subgroup of the consequence-based compensation methods is passive CB, such as electrode shorting by discharge resistors [27, 55], shown in Fig. 3.4. However, its success and compensation current intensities are not controlled [40]. They depend on the amount of residual charge, the time available for discharge and its time constant, defined by the electrode impedance and discharge resistance [40, 56]. Especially, considering multi-channel FES, passive CB brings disadvantages not only in terms of size but also in efficacy [40, 56]. For example, the effectiveness of stimulation is reduced in case that one channel is stimulated, while an adjacent channel is shorted to  $V_{\rm CM}$ , thus creating and unwanted current path through a second electrode [56]. Additionally, several electrodes shorted simultaneously to  $V_{\rm CM}$ , distribute their charges among each other in an uncontrolled manner, in which current peaks might trigger action potentials. Further, HV stimulation also requires HV-robust CB circuits. Thus, even simple solutions like electrode shorting bring along challenges, i.e. the lack of HV switches [5, 40]. Therefore, in chapter 4, this work gives a solution for passive CB via a HV-robust switch.

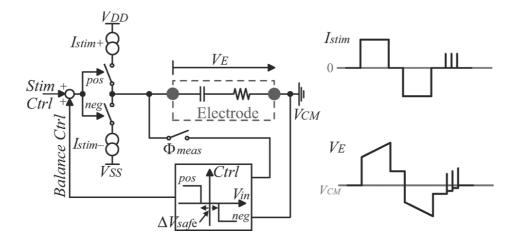

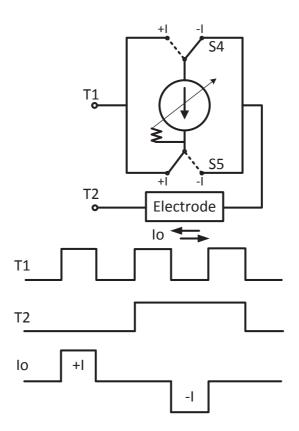

#### 3.2.2. Short Pulse Insertion

One subgroup of consequence-based CB is short pulse insertion of a fixed amount of charge [4, 6, 9, 48]. In between the stimulation periods, the residual electrode voltage  $V_{\rm E}$  is monitored and compared to the predefined safety limits. Once the safety limit is exceeded, short current pulses are inserted into the electrode, as shown in Fig. 3.5. In [6] for example, the pulses have an amplitude of  $\pm 20\,\mu\text{A}$  and a width of 20  $\mu$ s. The duration of the required balancing period is estimated by an off-chip microcontroller.

**Figure 3.5.:** Short pulse insertion charge balancing and its waveforms. Taken from [9] (©2010, IEEE).

In addition to control units, further components like comparators are necessary to determine the safety limits and the direction of compensation.

Short pulse insertion is further examined in [9]: "Nonetheless, the effect of the inserted short pulses on an unwanted neural stimulation has not been proven yet. In addition, the required number of balancing current pulses and, therewith, the duration of the charge balancing depends on the actual charge imbalance after each stimulation. Vice versa, the maximum amount of mismatch charge, which can be compensated, depends on the adjusted charge per pulse and the number of pulses allowed over time." The pulse insertion control loop is stable and the electrode potential is settled within the safe range only, if the time between two stimulations is long enough to fit the required number of balancing pulses and if the charge of these pulses is small enough not to exceed the safety range.

# 3.3. Cause-Based Charge Balancing Methods

Cause-based compensation methods aim to mitigate the origin of the charge mismatch within the stimulator. Instead of an instantaneous charge compensation, a long-term balanced condition is reached by charge correction of the cathodic and anodic stimulus. Thereby, the amplitude or pulse width of the stimuli are adjusted by a preceding settling process with possible overshoots during startup. The two subgroups stimulus matching and offset compensation differ in their reference for successful compensation, which is the surveillance of the transferred charges or the residue electrode voltage, respectively.

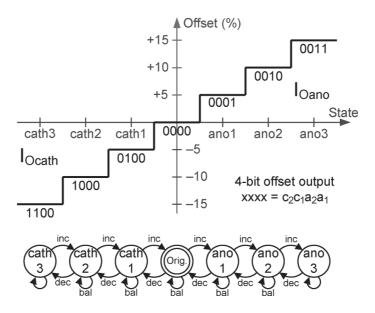

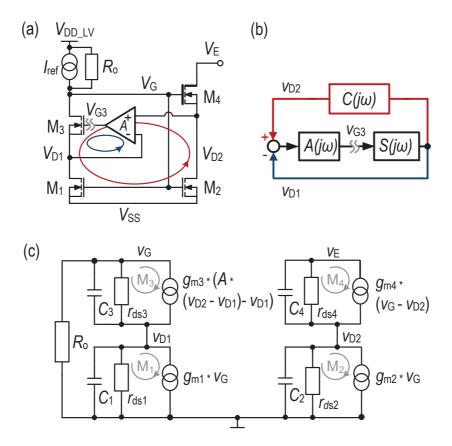

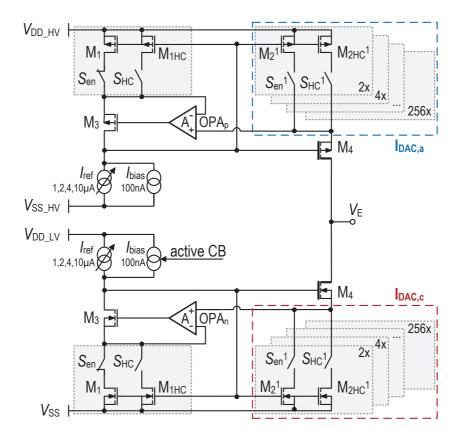

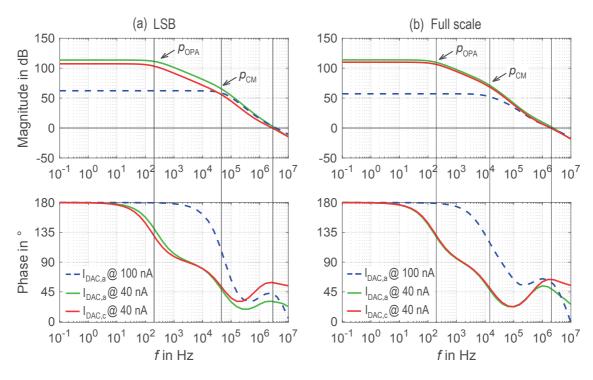

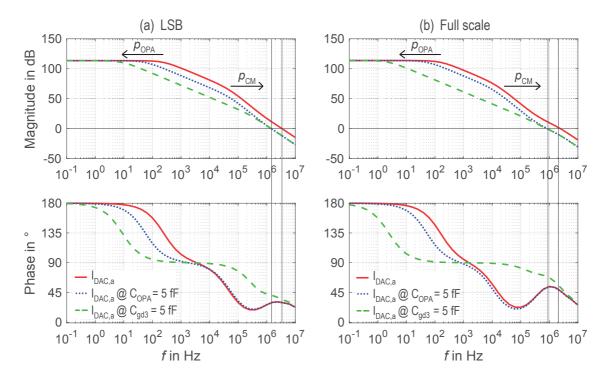

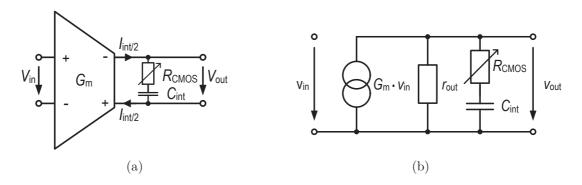

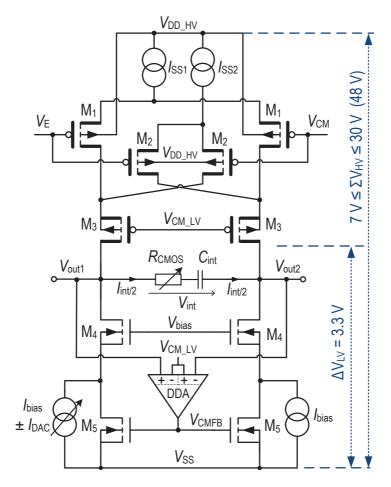

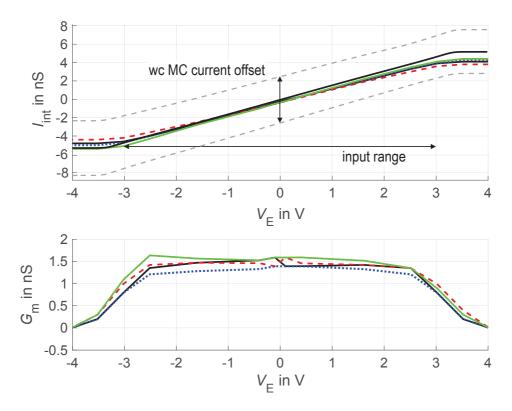

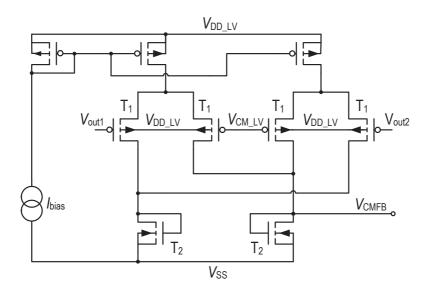

#### 3.3.1. Stimulus Matching